电 子 线 路 设 计 与 测 试 实 验 报 告 一、实验名称 多功能数字钟设计 二、 实验目的 1

掌握可编程逻辑器件的应用开发技术 ——设计输入、编译、仿真和器件编程; 2

熟悉一种 EDA 软件使用; 3

掌握Verilog 设计方法; 4

掌握分模块分层次的设计方法; 5

用Verilog 完成一个多功能数字钟设计

三、 设计内容及要求 1.基本功能 ➢ 具有“秒”、“分”、“时”计时功能,小时按 24 小时制计时

➢ 具有校时功能,能对“分”和“小时”进行调整

扩展功能 ➢ 仿广播电台正点报时

在 59 分51 秒、53 秒、55 秒、57 秒发出低音 512Hz信号,在 59 分59 秒时发出一次高音 1024Hz 信号,音响持续 1 秒钟,在1024Hz 音响结束时刻为整点

➢ 定时控制,其时间为 23 时 58 分

选做内容 ➢ 任意时刻闹钟(闹钟时间可设置)

➢ 自动报整点时数

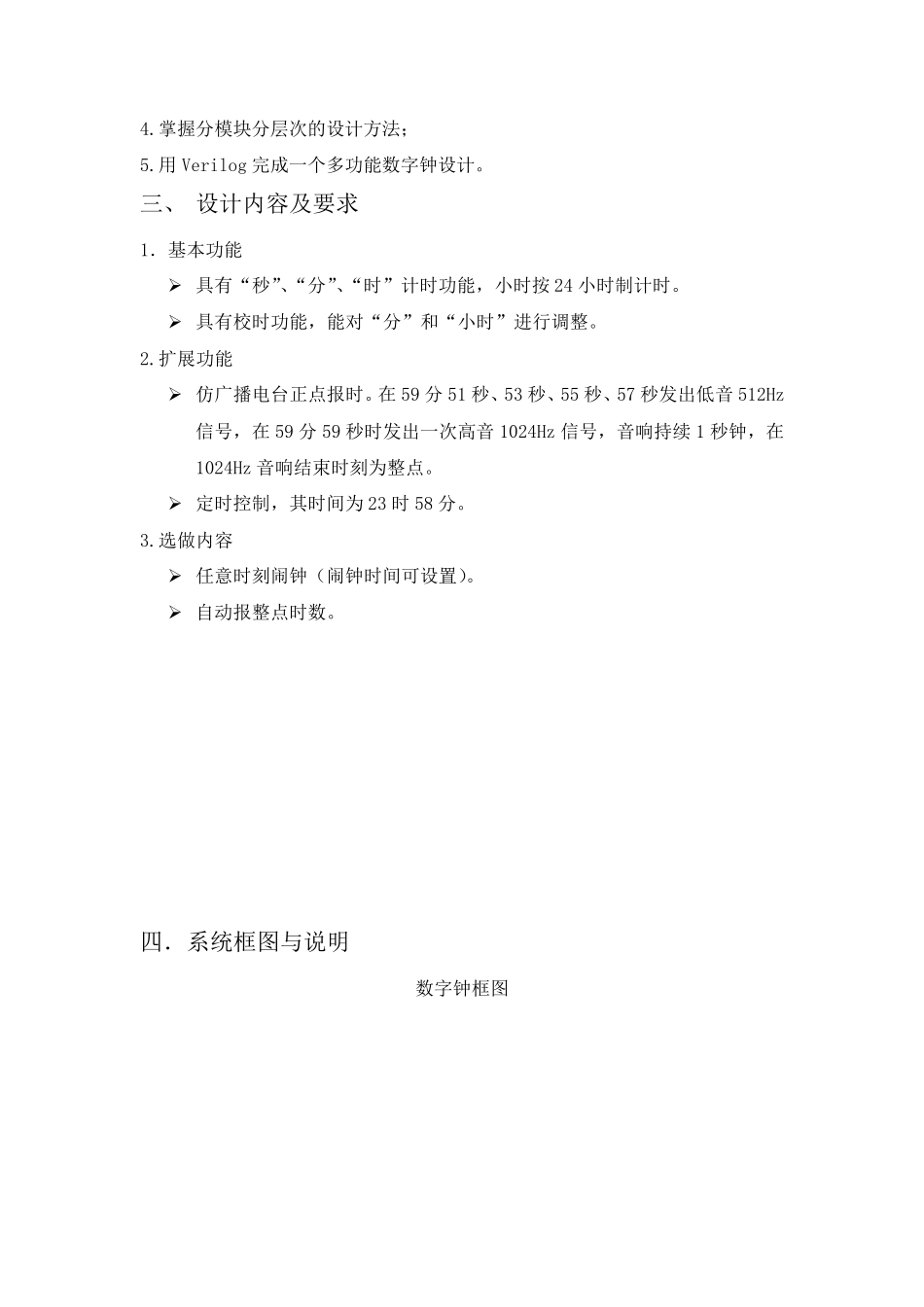

四.系统框图与说明 数字钟框图 1

数字钟电路系统由主体电路和扩展电路两大部分所组成

秒计数器计满60 后向分计数器进位,分计数器计满60 后向小时计数器进位,小时计数器按照“24 进制”规律计数

计数器的输出经译码器送显示器

五. 设计步骤 1

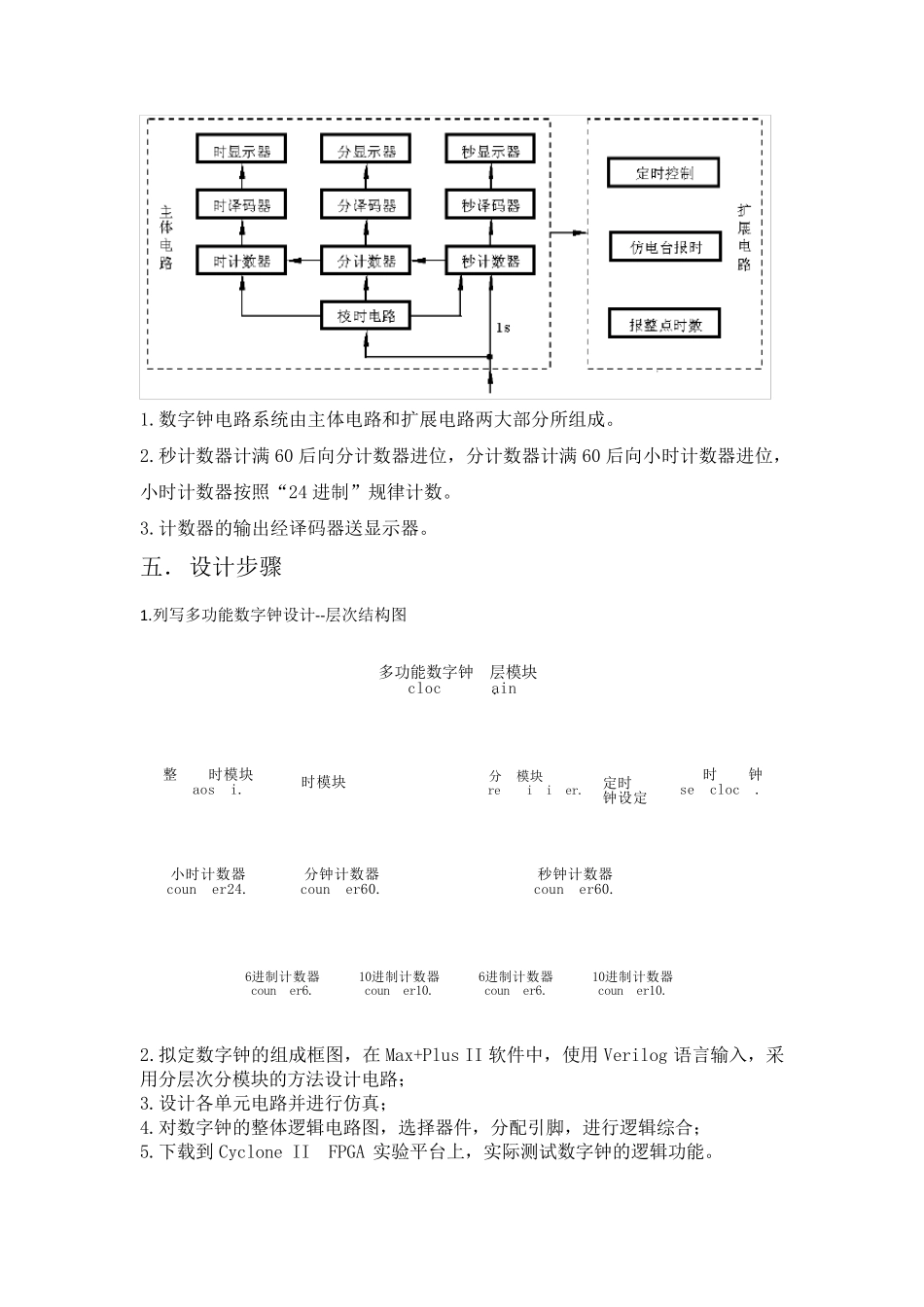

列写多功能数字钟设计--层次结构图 多功能数字钟顶层模块(clock_main

v)小时计数器(counter24

v)分钟计数器(counter60

v)秒钟计数器(counter60

v)6进制计数器(counter6

v)10进制计数器(counter10

v)6进制计数器(counter6

v)10进制计数器(counter10

v)分频模块(fre_divider

v)固定时刻闹钟设定校时模块任意时刻闹钟(setclock

v)整点报时模块(baoshi

拟定数字钟的组成框图,在