数字逻辑电路实验报告 电子7 2 班0 7 0 5 1 0 4 2 冯天宇 1 数字逻辑电路实验报告 ——计数器设计与应用 学院:电 信 学 院 班级:电子 72 班 姓名:*** 学号:******** 日期:2009 年 12 月 31 日 数字逻辑电路实验报告 电子7 2 班0 7 0 5 1 0 4 2 冯天宇 2 一、实验目的: 1

全面、系统的认识与提高《数字逻辑》课程的学习

熟悉和掌握EDA 软件(Quartus II 6

0)设计调试电路的方法

通过实验,提高运用数字逻辑电路解决实际问题的能力,并使学生更深入的理解所学知识

用D 触发器设计同步十六进制加法计数器

用74LS163(同步清零)设计一个六十进制计数器

6.用74LS163 或74LS190 设计24 小时制计时器

二、设计电路及说明: 1

用D 触发器设计同步十六进制加法计数器

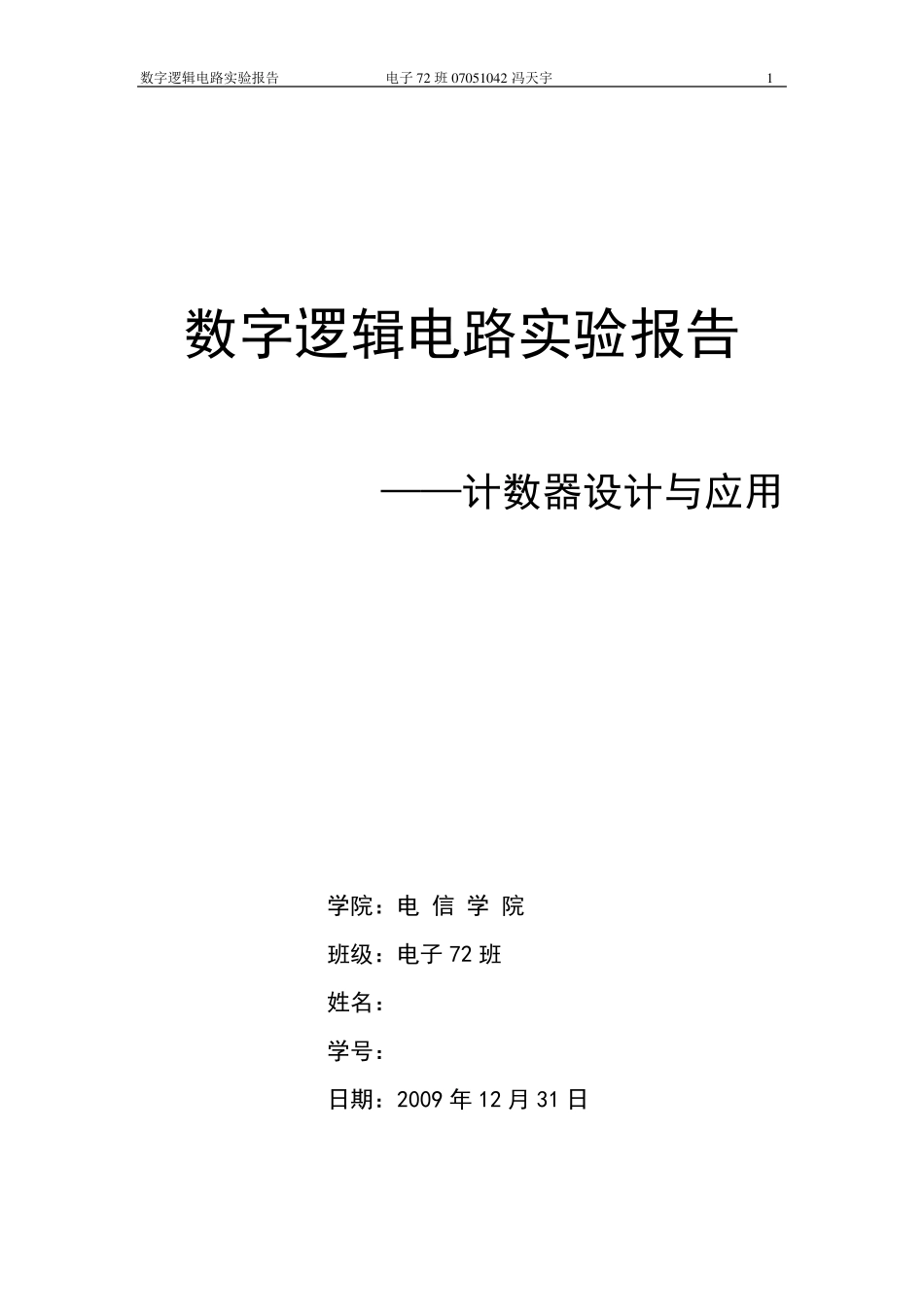

电路如下: 所用器件:2 个或门,3 个异或门,1 个非门,4 个D 触发器

同步计数器中,所有触发器的时钟输入端均接受统一计数脉冲并同时产生进位信号,进位信号需要用控制门加以控制

图中:D1=/Q1 D2=Q1○+Q2 D3=(Q2·Q1) ○+Q3 D4=(Q3·Q2·Q1) ○+Q4 数字逻辑电路实验报告 电子7 2 班0 7 0 5 1 0 4 2 冯天宇 3 从上述D 的表达式可以看出,当Qi-1,Qi-2,……,Q1均为 1 时,再来一个计数脉冲,则产生至第 i 位触发器的进位信号,Qi将变反;否则 Qi保持不变

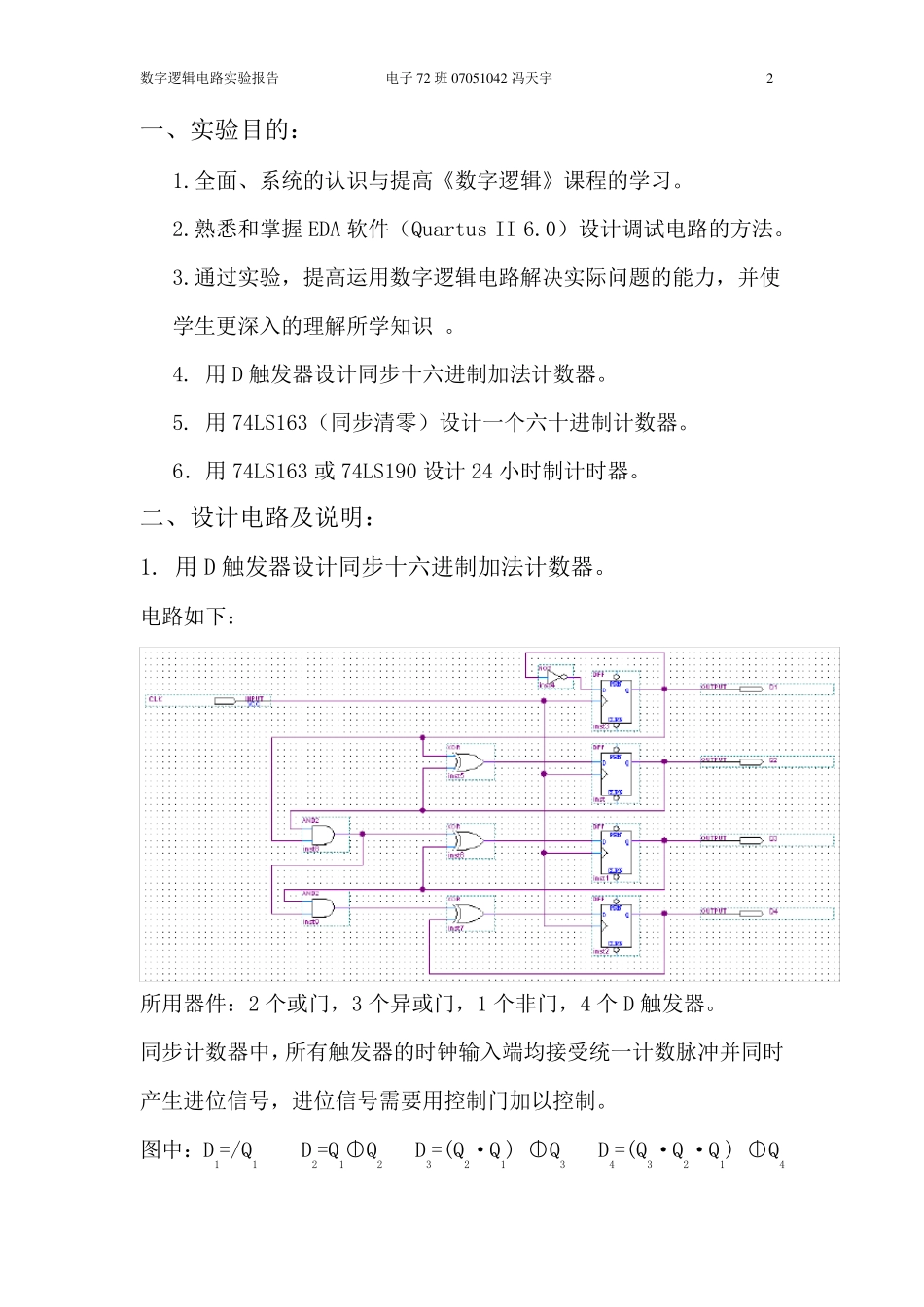

仿真结果如下: 2

用 74LS163(同步清零)设计一个六十进制计数器: 电路如下: 数字逻辑电路实验报告 电子7 2 班0 7 0 5 1 0 4 2 冯天宇 4 所用器件:2 个与非门,2 个74LS163 同步计数器

说明: 74LS163 是