《数字电子技术课程设计》报告 题目:数字钟电路设计 指导教师: 班 级: ******* 姓 名 :****** 学 号:20***31034 山东****学院 时 间:2006年 1月 16日至1月 20日 目录 数字电子技术课程设计 报告 1 数字钟电路设计 1 【设计题目】 3 【设计目的】 3 【设计指标及要求】 3 【设计原理】 3 1

总体设计方案 3 2

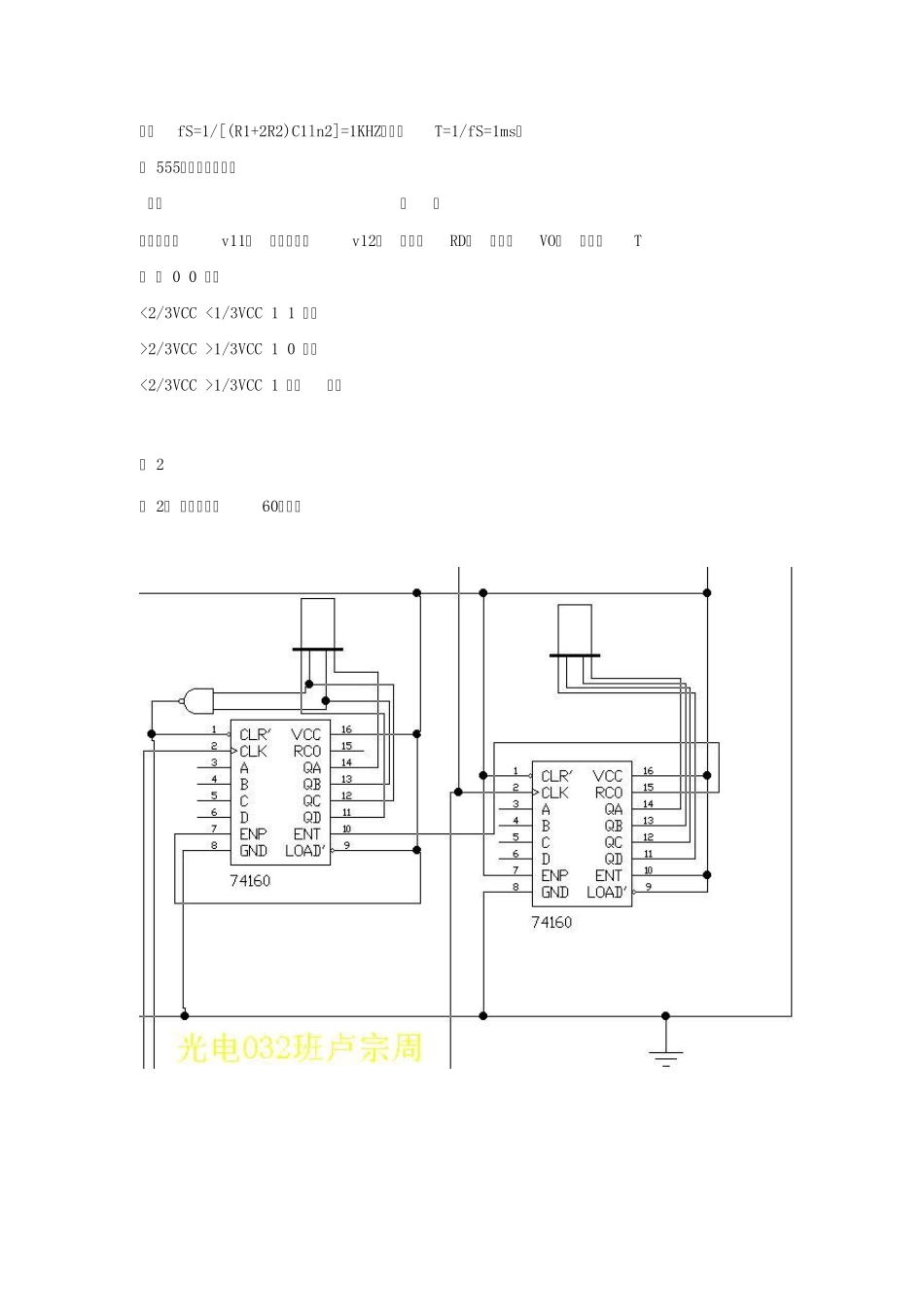

对于各个部分而言 3 3

各独立功能部件的设计 4 ( 1) 振荡器 4 ( 2)秒计时器(60进制) 5 ( 3)时间校对电路 6 4系统电路图 8 5计时仿真图 8 【安装和调试】 9 【元件清单】 9 【设计收获】 10 【参考文献】 10 【设计题目】 多功能数字钟的设计 【设计目的】 1掌握数字系统的分析和设计方法 2能够熟练的、合理的选用集成电路器件 3熟悉EWB 软件的使用

【设计指标及要求】 设计一个多功能数字钟,以一昼夜24小时为一个计数周期

准确计时,具有“时”“分”“秒”数字显示

整点能自动打点、报时

要求报时声响四低一高,最后一响为整点

具有校时功能

要求电路主要采用中小规模CMOS 集成电路

要求电路尽量简化,并选用同类型的器件

在EWB 电子工作平台上进行电路的设计和计算机仿真

【设计原理】 1

总体设计方案 数字钟原理框图如图1所示,电路一般包括以下几个部分:振荡器、分频器、译码显示电路、时分秒计数器、校时电路、报时电路以及闹铃电路

图 1 数字钟原理框图 2

对于各个部分而言 数字钟计时的标准信号应该是频率相当稳定的1HZ 秒脉冲,所以要设置标准时间源

数字钟计时周期是24,因此必须设置24计数器,秒、分、时由七段数码管显示

为使数字钟走时与标准时间一致,校时电路是必不可少的

设计中采用开关控制校时直接用秒脉冲先后对“时”“分”“秒”计数器进行校时操作