Cadence Allegro 元件封装制作流程1

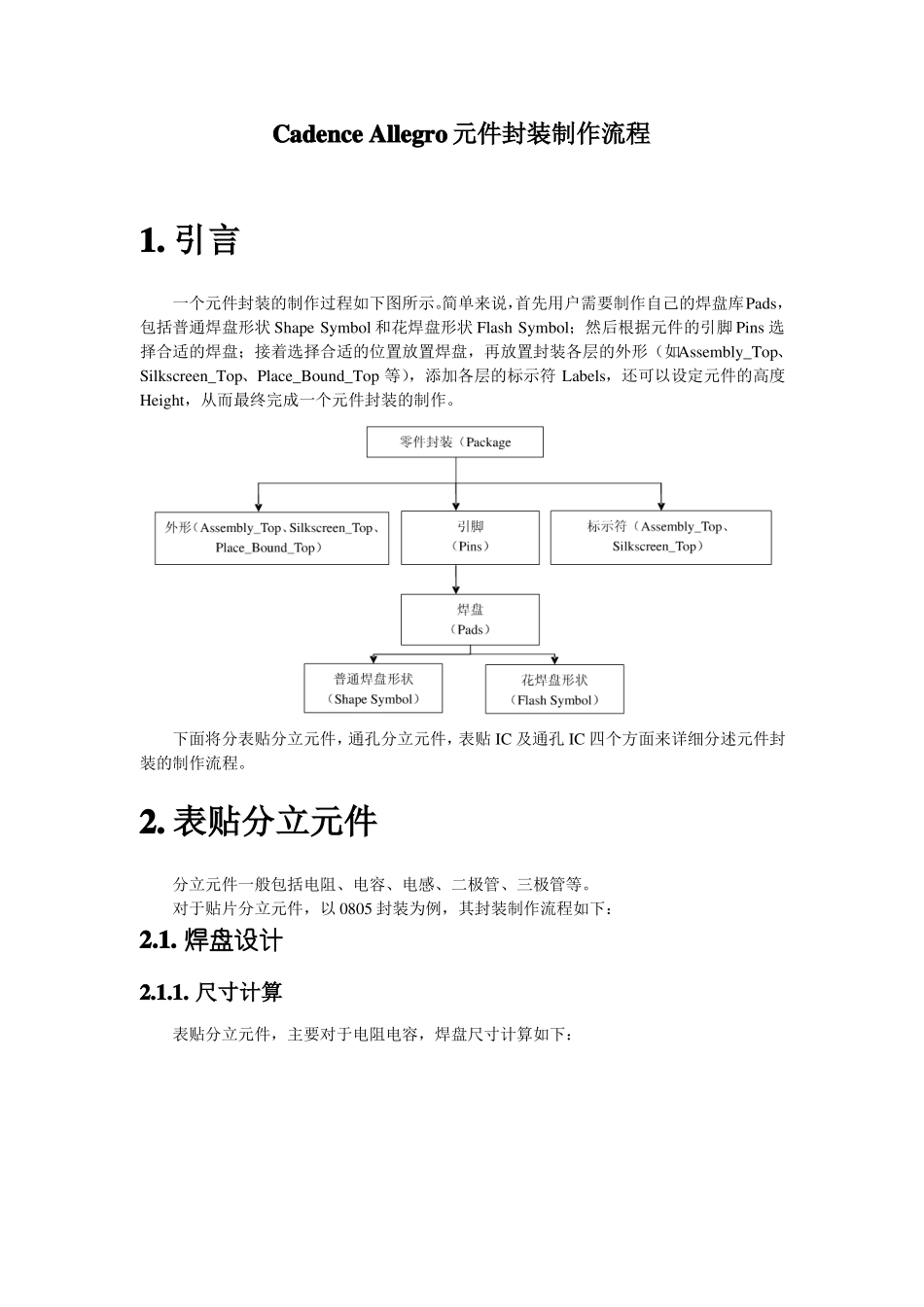

引言一个元件封装的制作过程如下图所示

简单来说,首先用户需要制作自己的焊盘库Pads,包括普通焊盘形状 Shape Symbol 和花焊盘形状 Flash Symbol;然后根据元件的引脚 Pins 选择合适的焊盘;接着选择合适的位置放置焊盘,再放置封装各层的外形(如Assembly_Top、Silkscreen_Top、Place_Bound_Top 等),添加各层的标示符 Labels,还可以设定元件的高度Height,从而最终完成一个元件封装的制作

下面将分表贴分立元件,通孔分立元件,表贴 IC 及通孔 IC 四个方面来详细分述元件封装的制作流程

表贴分立元件分立元件一般包括电阻、电容、电感、二极管、三极管等

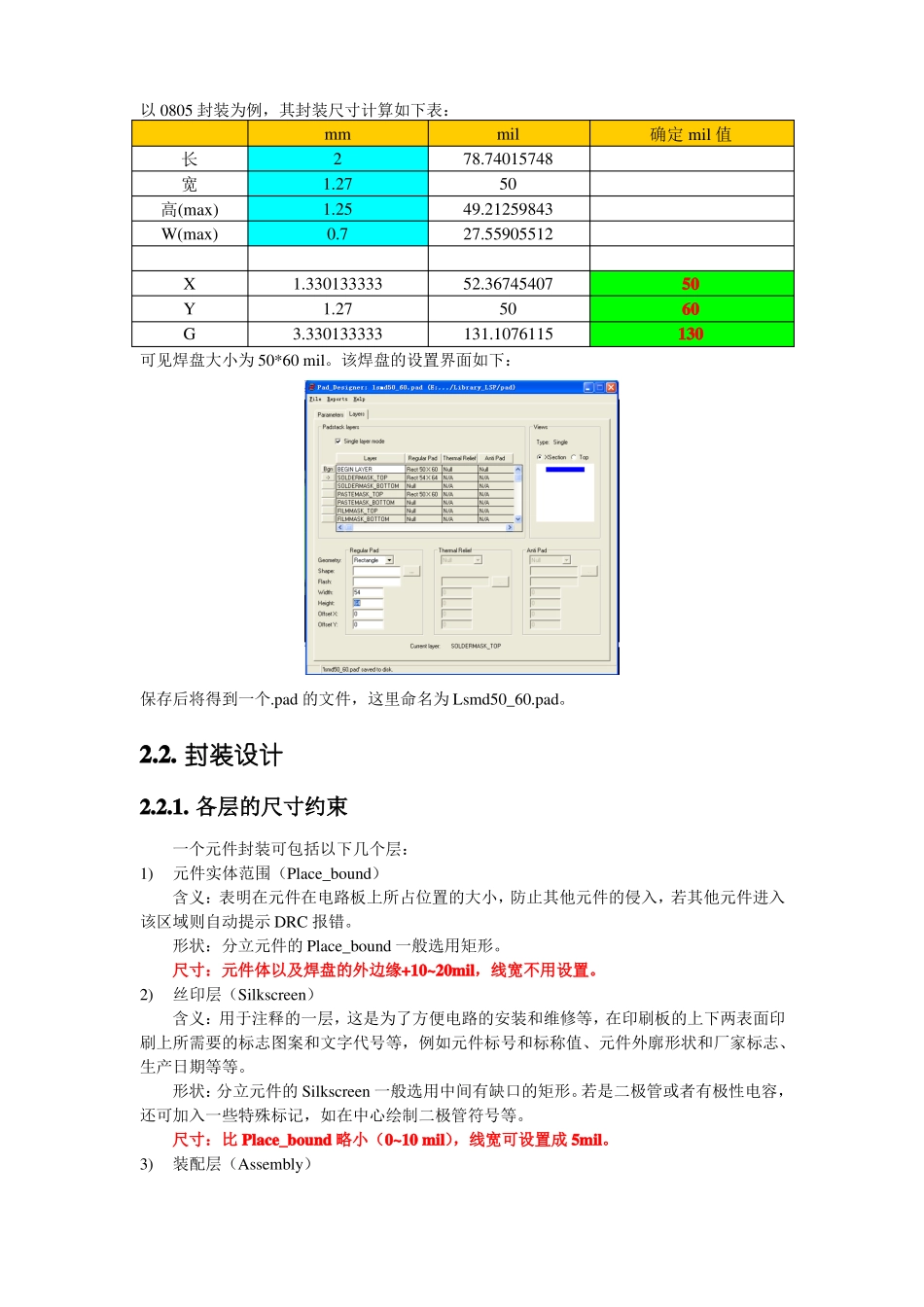

对于贴片分立元件,以 0805 封装为例,其封装制作流程如下:2

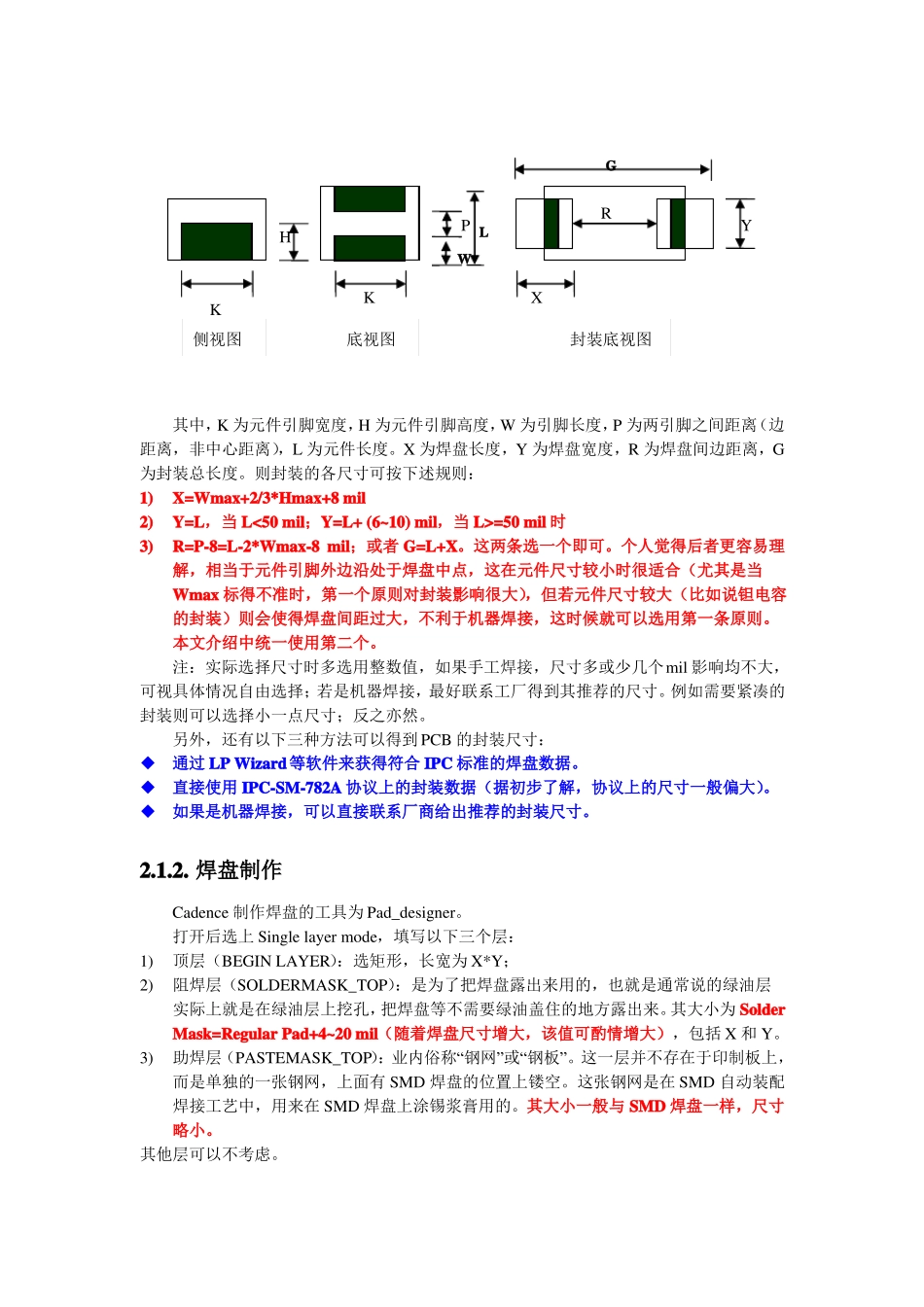

尺寸计算表贴分立元件,主要对于电阻电容,焊盘尺寸计算如下:GHP LWRYK侧视图K底视图X封装底视图其中,K 为元件引脚宽度,H 为元件引脚高度,W 为引脚长度,P 为两引脚之间距离(边距离,非中心距离),L 为元件长度

X 为焊盘长度,Y 为焊盘宽度,R 为焊盘间边距离,G为封装总长度

则封装的各尺寸可按下述规则:1)X=Wmax+2/3*Hmax+8 mil2)Y=L,当 L=50 mil 时3)R=P-8=L-2*Wmax-8 mil;或者 G=L+X

这两条选一个即可

个人觉得后者更容易理解,相当于元件引脚外边沿处于焊盘中点,这在元件尺寸较小时很适合(尤其是当Wmax 标得不准时,第一个原则对封装影响很大),但若元件尺寸较大(比如说钽电容的封装)则会使得焊盘间距过大,不利于机器焊接,这时候就可以选用第一条原则

本文介绍中统一使用第二个

注:实际选择尺寸时多选用整数值,如果手工焊接,尺寸多或少几个mil