基于 EDA 的数字秒表设计论文班级:同组人员:孙兴义电信二班 20111060223张忠义 2011106024011基于 EDA 的数字秒表设计摘要:该设计是用于体育比赛的数字秒表,基于 EDA 在 Quartus II 9

0sp2软件下应用 VHDL 语言编写程序,采用 ALTRA 公司 CycloneII 系列的 EP2C8Q208芯片进行了计算机仿真,并给出了相应的仿真结果

本设计有效的克服了传统的数字秒表的缺点采用 EDA 技术采取自上而下的设计思路

绘制出了具体的逻辑电路,最后又通过硬件上对其进行调试和验证

该电路能够实现很好的计时功能,计时精度高,最长计时时间可达一个小时

关键字:数字秒表;EDA;FPGA;VHDL;Quartus II1 引言在科技高度发展的今天,集成电路和计算机应用得到了高速发展

尤其是计算机应用的发展

它在人们日常生活已逐渐崭露头角

大多数电子产品多是由计算机电路组成,如:手机、mp3 等

而且将来的不久他们的身影将会更频繁的出现在我们身边

各种家用电器多会实现微电脑技术

电脑各部分在工作时多是一时间为基准的

本文就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字秒表[1]

秒表在很多领域充当一个重要的角色

在各种比赛中对秒表的精确度要求很高,尤其是一些科学实验

他们对时间精确度达到了几纳秒级别

2 设计要求(1) 能对 0 秒~59 分 59

99 秒范围进行计时,显示最长时间是 59 分 59 秒;(2) 计时精度达到 0

01s;(3) 设计复位开关和启停开关,复位开关可以在任何情况下使用,使用以后计时器清零,并做好下一次计时的准备

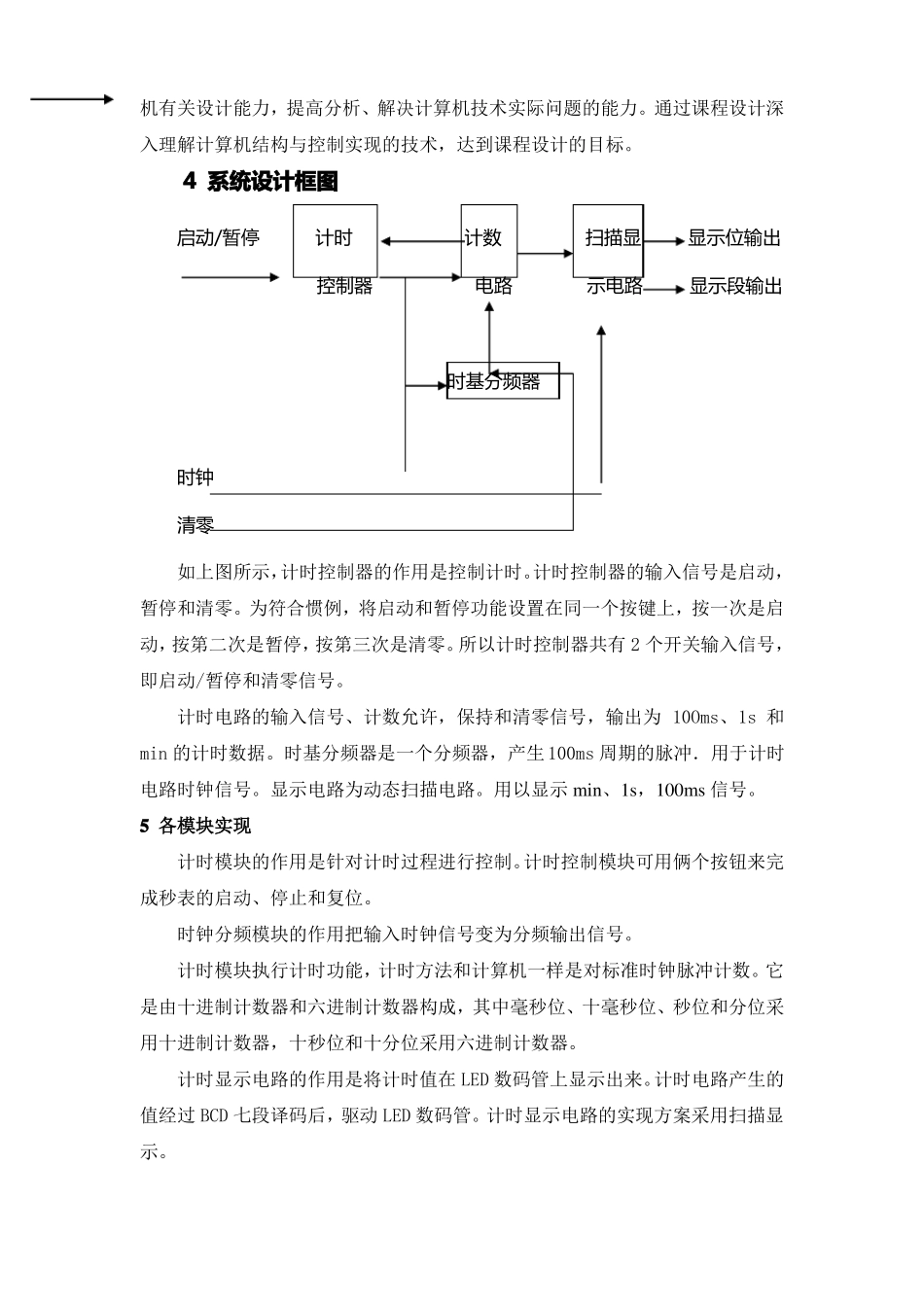

设计由控制模块、时基分频模块,计时模块和显示模块四部分组成

各模块实现秒表不同的功能3 数字秒表设计的目的本次设计的目的就是在掌握 EDA 实验开发系统的初步使用基础上,了解EDA 技术