SDR SDRAMMT48LC128M4A2 – 32 Meg x 4 x 4 banksMT48LC64M8A2 – 16 Meg x 8 x 4 banksMT48LC32M16A2 – 8 Meg x 16 x 4 banksFeatures• PC100- and PC133-compliant• Fully synchronous; all signals registered on positiveedge of system clock• Internal, pipelined operation; column address canbe changed every clock cycle• Internal banks for hiding row access/precharge• Programmable burst lengths: 1, 2, 4, 8, or full page• Auto precharge, includes concurrent auto pre-charge and auto refresh modes• Self refresh mode• Auto refresh–64ms, 8192-cycle (commercial and industrial)• LVTTL-compatible inputs and outputs• Single +3

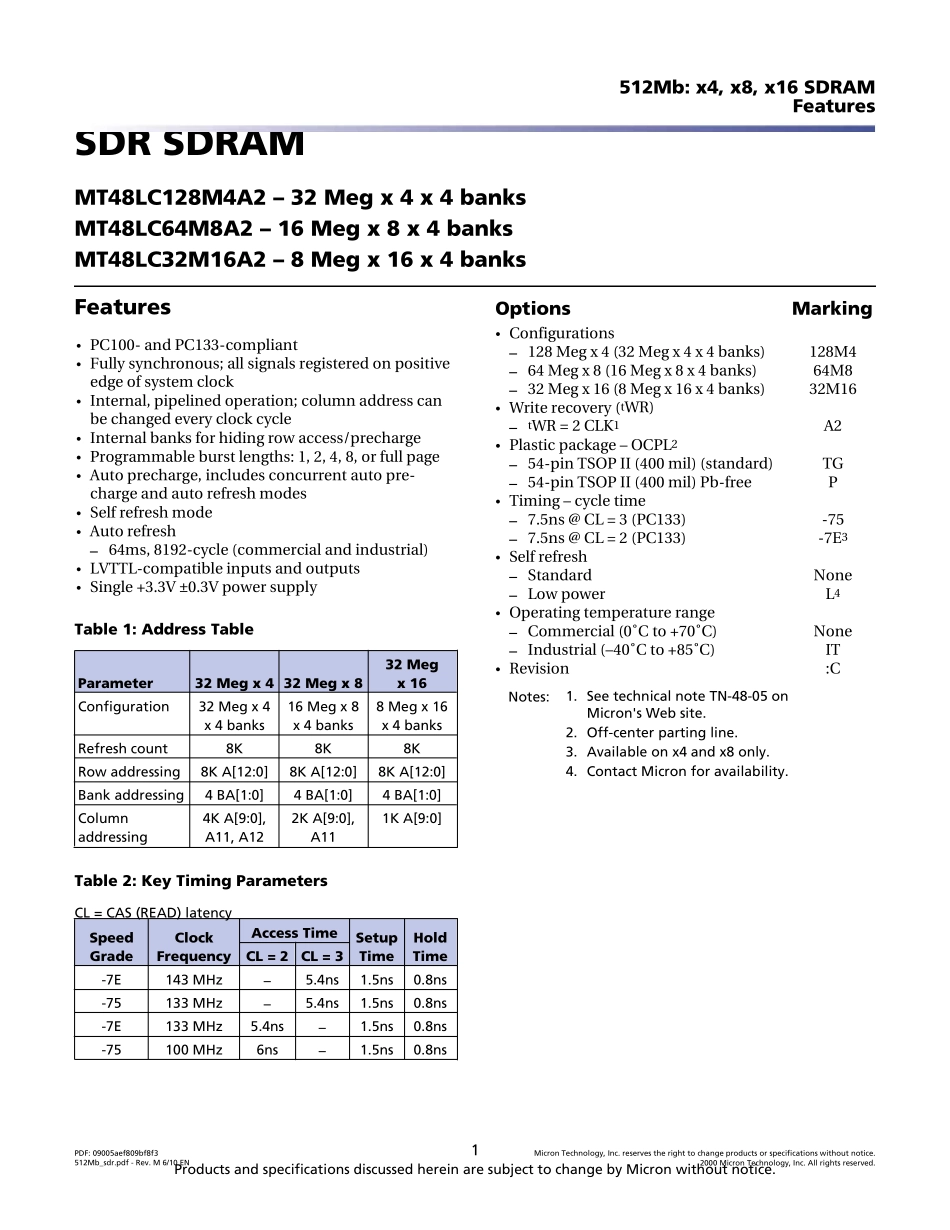

3V power supplyTable 1: Address TableParameter32 Meg x 4 32 Meg x 832 Megx 16Configuration32 Meg x 4x 4 banks16 Meg x 8x 4 banks8 Meg x 16x 4 banksRefresh count8K8K8KRow addressing8K