28335 之系统时钟 本系列文章由斌斌-龙臻(Mr_D_prince)独立完成,首发于QQ 空间,会在百度空间、网易博客同步更新,转载必须注明作者和出处,必须注明原文链接

注:本系列文章主要针对 TI 公司的 C28x x 系列DSP 芯片的一些功能模块进行介绍,并描述基本的配置

文章中提到的 DSP 芯片未说明即默认为 TMS320F28335,简称为 28335

28335 的系统时钟主要包括锁相环(PLL)、看门狗(WatchDog)、外部时钟(PeripheralClock)等几个模块

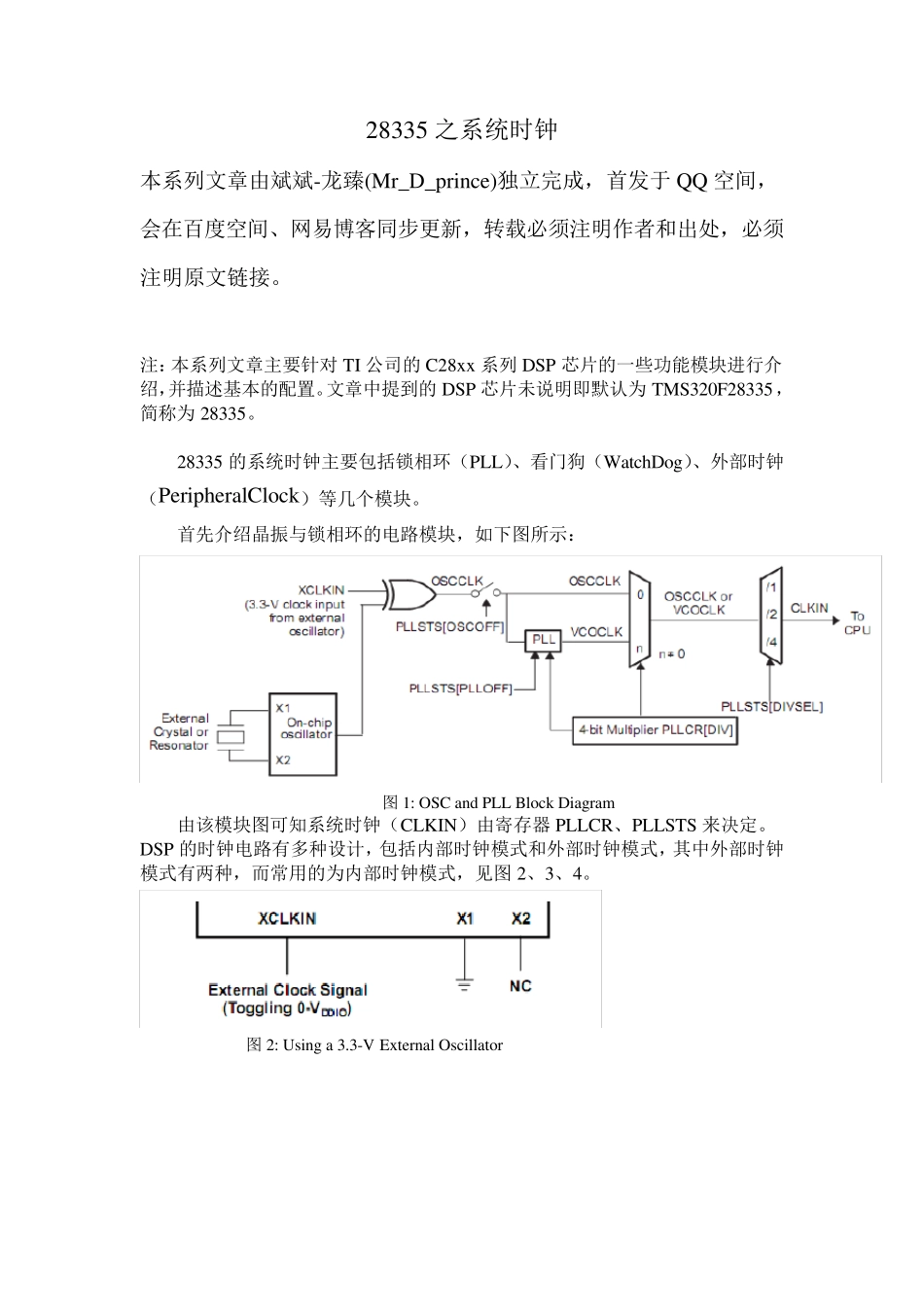

首先介绍晶振与锁相环的电路模块,如下图所示: 图 1: OSC and PLL Block Diagram 由该模块图可知系统时钟(CLKIN)由寄存器 PLLCR、PLLSTS 来决定

DSP 的时钟电路有多种设计,包括内部时钟模式和外部时钟模式,其中外部时钟模式有两种,而常用的为内部时钟模式,见图 2、3、4

图 2: Using a 3

3-V Ex ternal Oscillator 图3:Using a 1

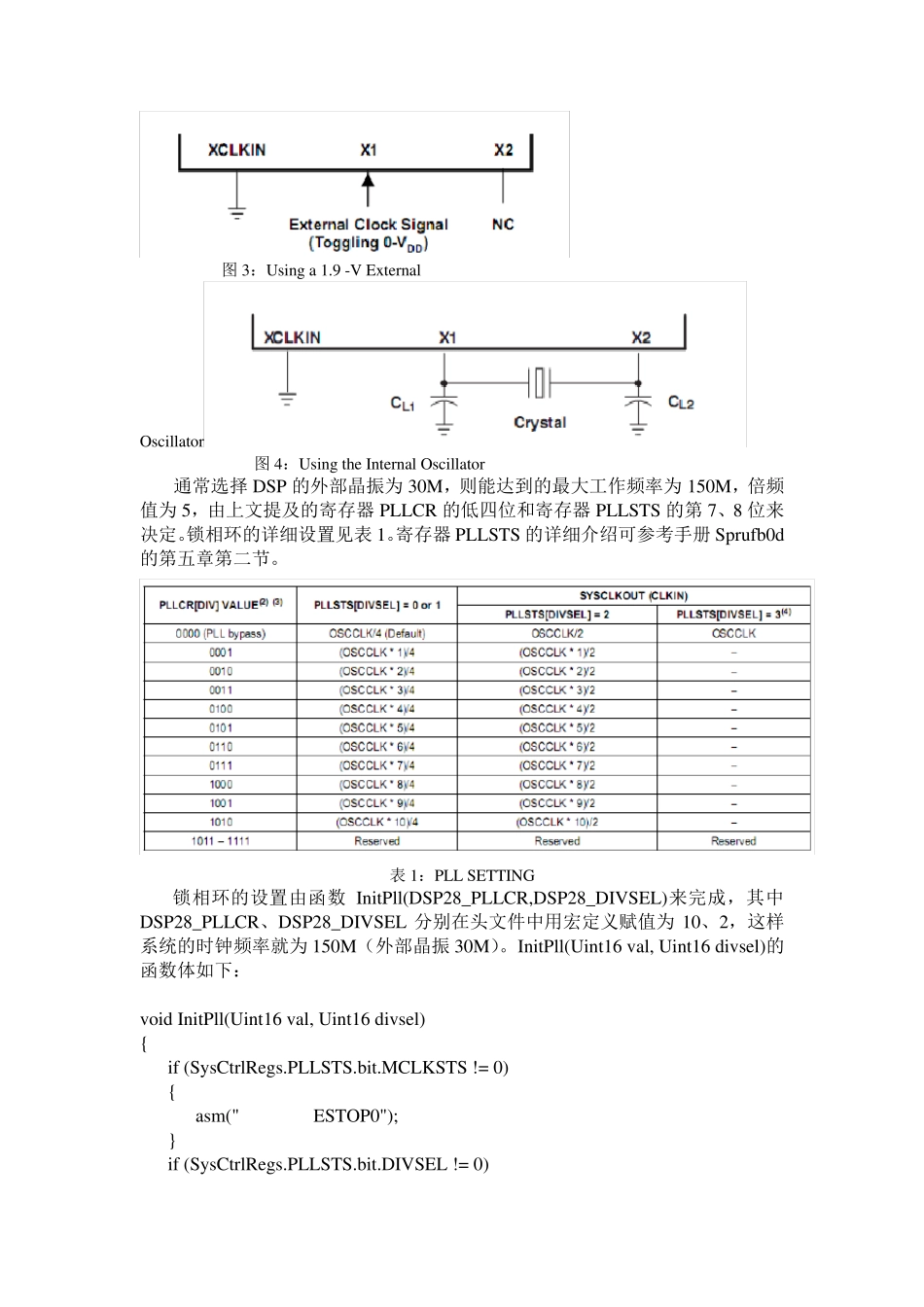

9 -V External Oscillator 图4:Using the Internal Oscillator 通常选择DSP 的外部晶振为30M,则能达到的最大工作频率为150M,倍频值为5,由上文提及的寄存器PLLCR 的低四位和寄存器PLLSTS 的第7、8 位来决定

锁相环的详细设置见表 1

寄存器PLLSTS 的详细介绍可参考手册 Sprufb0d的第五章第二节

表 1:PLL SETTING 锁相环的设置由函数 InitPll(DSP28_PLLCR,DSP28_DIVSEL)来完成,其中DSP28_PLLCR、DSP28_DIVSEL 分别在头文件中用宏定义赋值为10、2,这样系统的时钟频率就为150M(外部晶振30M)

InitPll(U