32 位Pow erPC 构架通用寄存器分析及总结三 4

6SR(Segment Registers)寄存器 OEA 定义了16 个32 位的SR 寄存器,段寄存器SR 可以使用mtsr/mfsr,mtsrin/mfsrin 指令进程访问

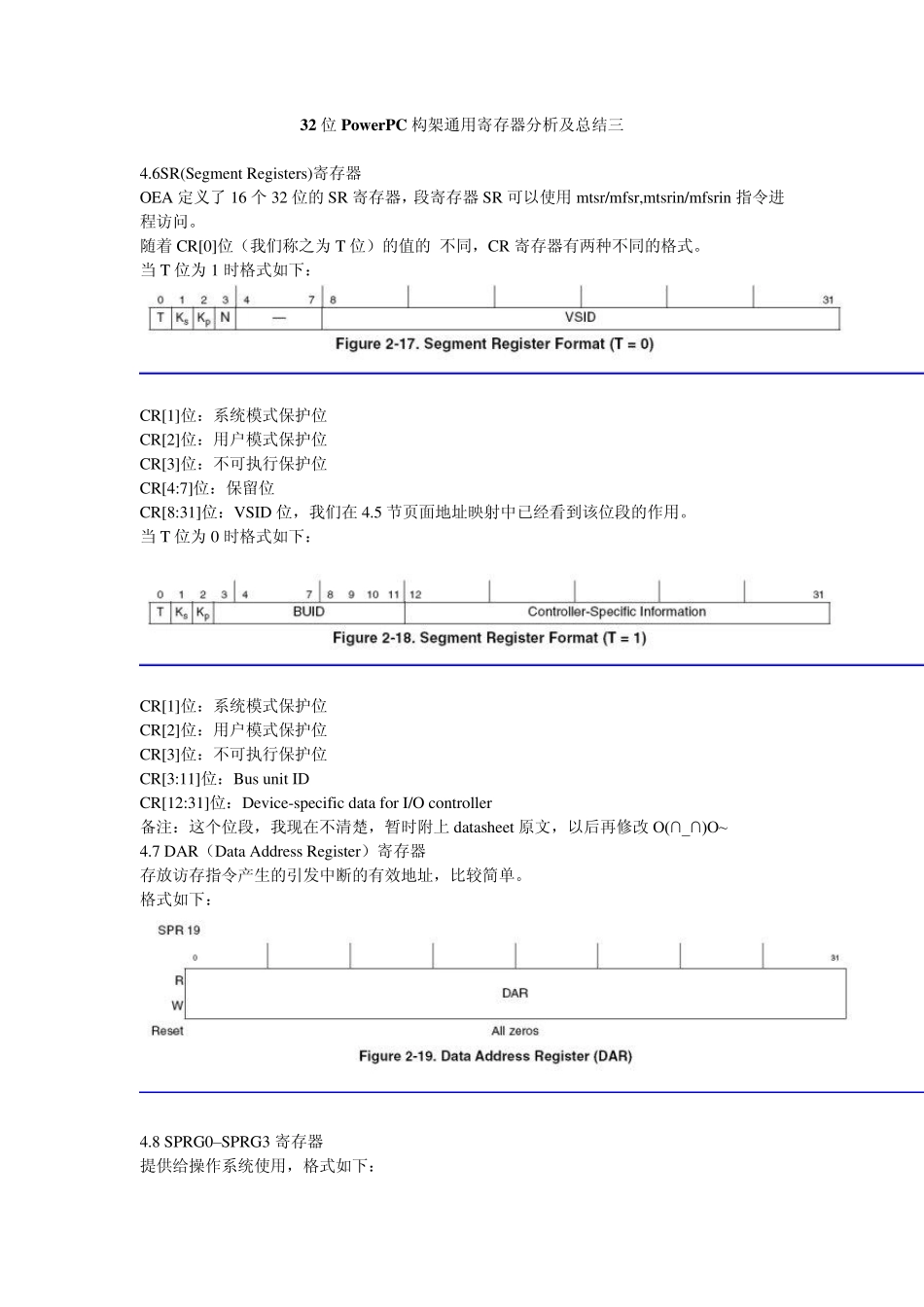

随着 CR[0]位(我们称之为 T 位)的值的 不同,CR 寄存器有两种不同的格式

当 T 位为 1 时格式如下: CR[1]位:系统模式保护位 CR[2]位:用户模式保护位 CR[3]位:不可执行保护位 CR[4:7]位:保留位 CR[8:31]位:VSID 位,我们在 4

5 节页面地址映射中已经看到该位段的作用

当 T 位为 0 时格式如下: CR[1]位:系统模式保护位 CR[2]位:用户模式保护位 CR[3]位:不可执行保护位 CR[3:11]位:Bu s u nit ID CR[12:31]位:Dev ice-specific data for I/O controller 备注:这个位段,我现在不清楚,暂时附上 datasheet 原文,以后再修改 O(∩_∩)O~ 4

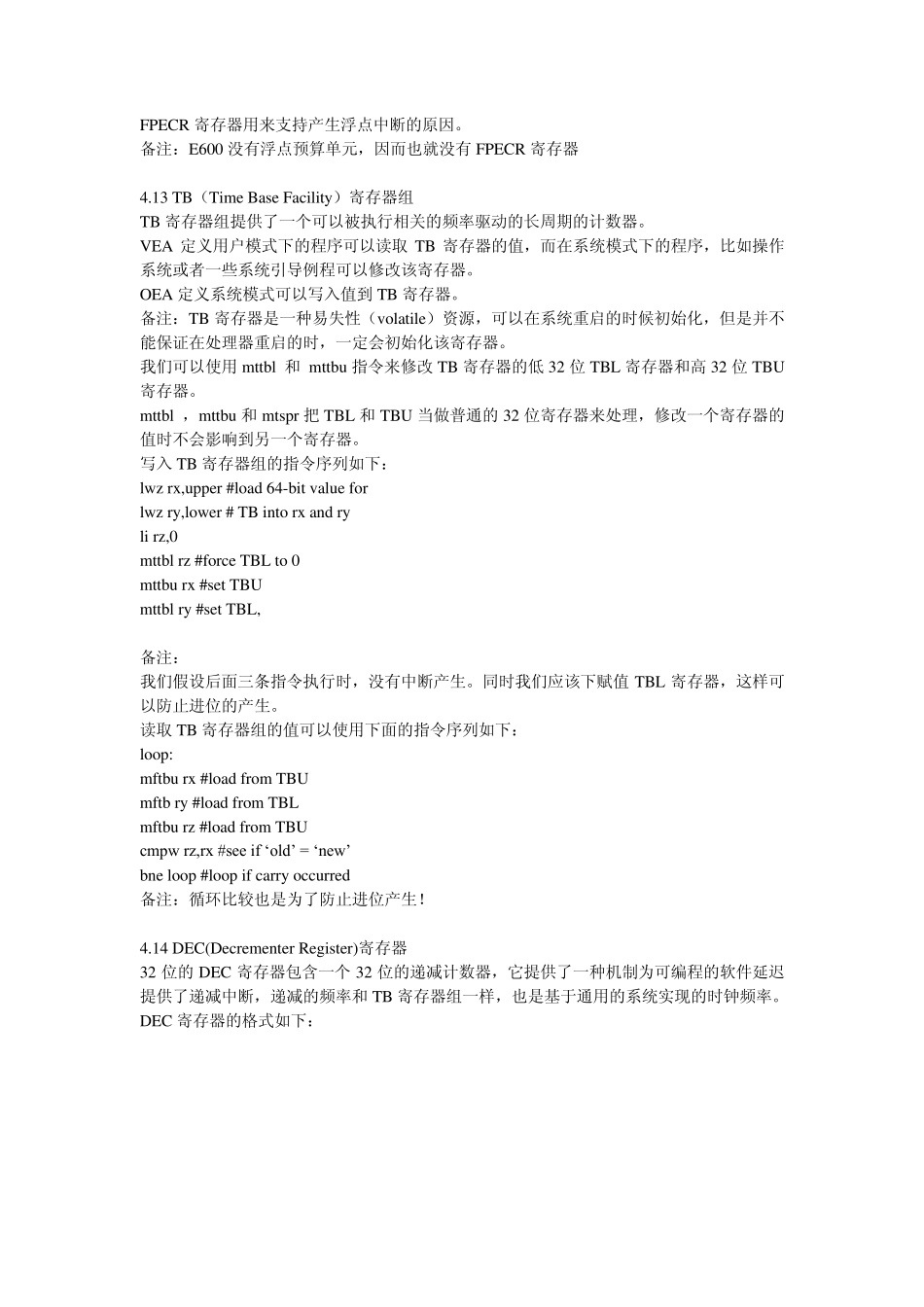

7 DAR(Data Address Register)寄存器 存放访存指令产生的引发中断的有效地址,比较简单

格式如下: 4

8 SPRG0–SPRG3 寄存器 提供给操作系统使用,格式如下: SPRG0:操作系统可能会加载一个独立的物理地址到该寄存器中,来标识一个内存区域是第一级的中断句柄专用的

SPRG2:可以被第一级的中断来保存通用寄存器的内容,该内容可以作为内存中保存其它通用寄存器的基地址

SPRG2 和 SPRG3 可以在操作系统需要时使用

备注:E600 有 8 个SPRGs 寄存器

9 DSISR 寄存器 用来决定 DSI 中断的中断源,格式如下: 4

10 SRR0(Machine Statu s Sav e/Resto