算术逻辑单元ALU 的设计 班 级:计科1201 班 学 号:********** * ***** 设计日期:2014-11-20 西安科技大学计算机科学与技术学院 1

实验题目 算数逻辑单元ALU 的设计 2

实验目的 设计一个简单的算数逻辑单元,并用Verilog 实现,得到仿真波形

实验设备 安装有modelsim 和Quartus2 的PC 机一台 4

实验原理 算术逻辑单元ALU 集成了各种算术运算和逻辑运算部件的功能,包括加、减、乘、除等数值运算、逻辑运算、移位运算等

把这些功能集成在一个逻辑部件ALU 之中,使得ALU 具有算术运算和逻辑运算功能

这种设计方法可以使得功能比较紧凑,简化对逻辑运算部件和算术运算部件的使用

同时还能最大限度的复用某些逻辑部件,从而减少逻辑电路的使用

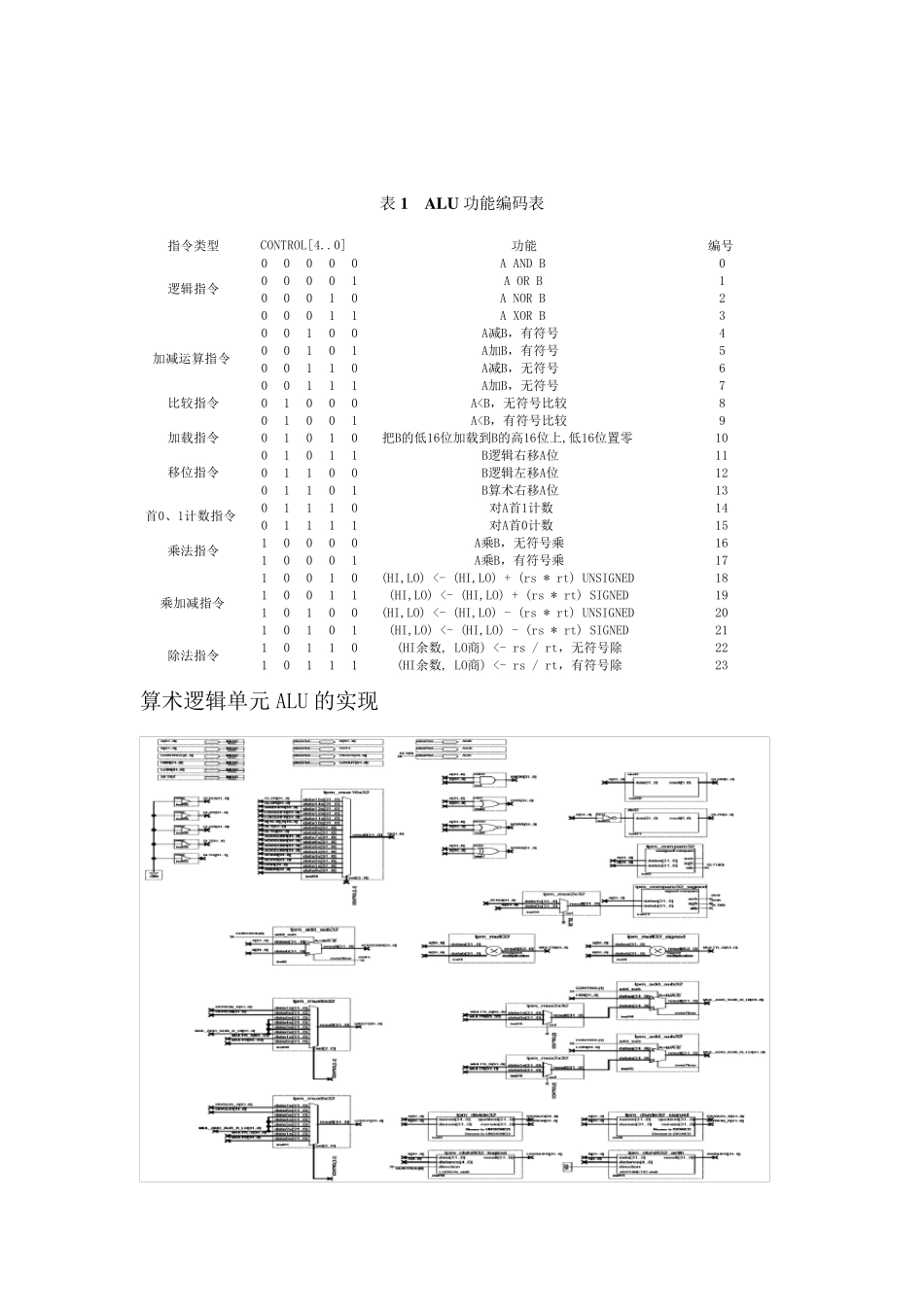

设计ALU 首先要对各种算数逻辑运算进行编码

表 1 为本文设计的处理器实用的ALU 功能编码表

表1 ALU 功能编码表 指令类型功能编号00000A AND B000001A OR B100010A NOR B200011A XOR B300100A减B,有符号400101A加B,有符号500110A减B,无符号600111A加B,无符号7比较指令 01000A