物理与电子工程学院 课程设计 题 目: 8 位十六进制频率计的设计 专 业: 应用电子技术教育 班 级: 0 7 姓 名: 学号: 实验地点: 指导老师: 成 绩: ( 2010

07 ) 8 位十六进制频率计的设计 1 引 言 现代电子设计技术的核心已日趋转向基于计算机的电子设计自动化技术,即EDA 技术

EDA 技术是依赖功能强大的计算机,在EDA 工具软件平台上,对以硬件描述语言HDL 为系统逻辑描述手段完成的设计文件,自动地完成编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能

而随着技术的进步,EDA 技术更多地应用到各个电子系统中已成一种趋势,本设计主要设计一 8 位十六进制频率计

1 设计内容 用 EDA 技术设计并实现8 位十六进制频率计

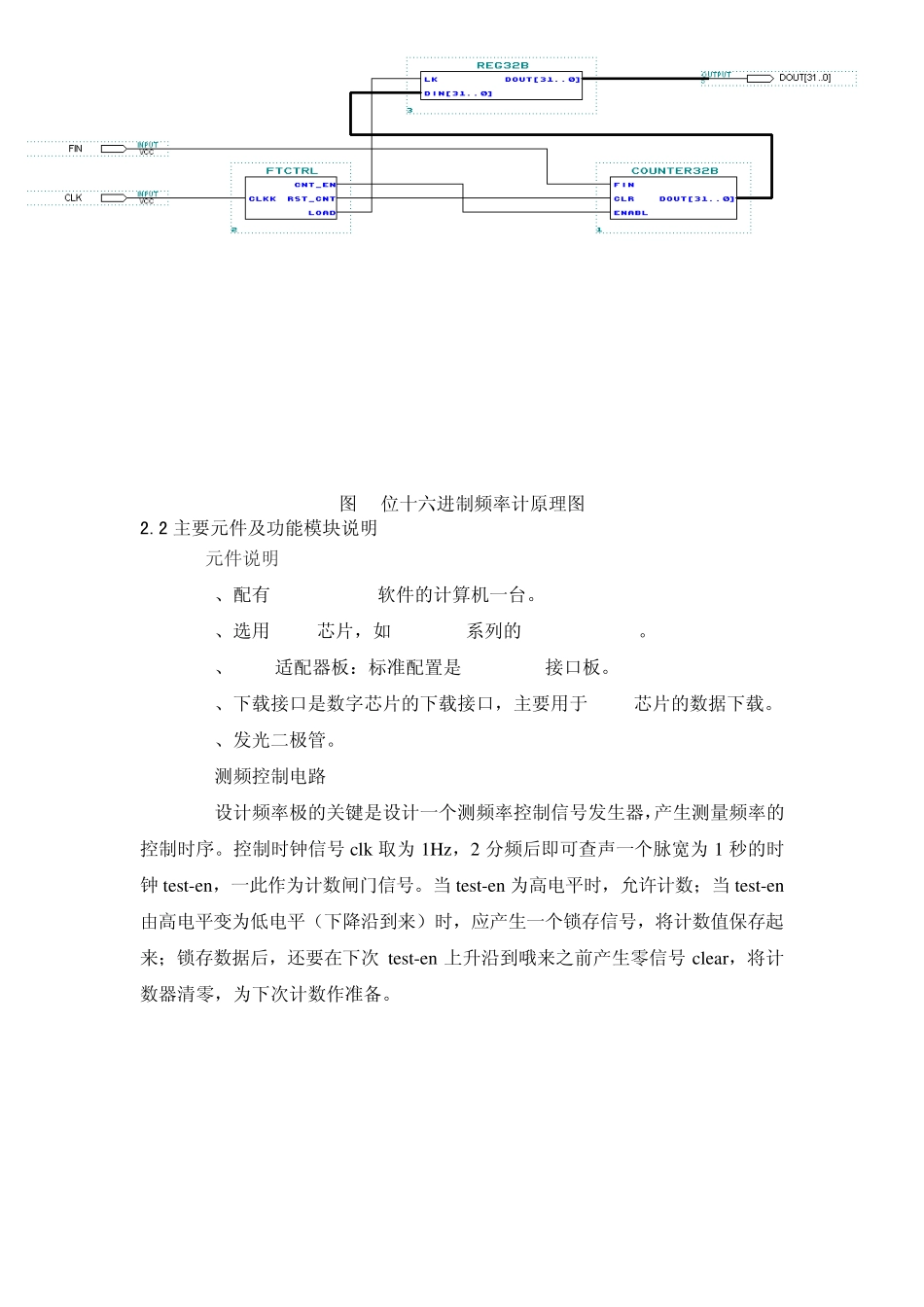

2 设计要求 (1)FTCTRL的计数使能信号 CNT_EN能产生一个 1秒脉宽的周期信号,并对频率计中的32位二进制计数器 COUNTER32B的ENABL使能进行同步控制

(2)当 CNT_EN高电平时允许计数;低电平时停止计数,并保持其所计的脉冲数

在停止计数期间,首先需要一个锁存信号 LOAD的上跳沿将计数器在前一秒钟的计数值锁存进各锁存器 REG32B中,并由外部的十六进制7段译码器译出,显示计数值

设置锁存器的好处是数据显示稳定,不会由于周期性的清零信号而不断闪烁

(3)锁存信号后,必须有清零信号 RST_CNT对计数器进行清零,为下一秒的计数操作作准备

3 系统主要功能 根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1 秒的输入信号脉冲计数允许的信号;1 秒计数结束后,计数值被锁入锁存器,计数器清零,为下一测频周期做好准备

测频控制信号可以由一个独立的发生器来发生

2 硬件设计 2

1原理电路图 图 8位十六进制频率计原理图 2