第五章 虚拟内存及缓冲区管理 在刚开始接触 TQ2440并测试 TEST程序时,当时就产生了一个疑惑,把程序下载到 NAND和 SDRAM中,其中断均能正确执行,当时以为,程序有可能采用了动态添加中断向量技术,即在 SDRAM中运行时在向量 0x18处添加跳转指令的二进制编码

虽然能够实现,但在实际编程时会非常麻烦

ARM采用了虚拟内存映射技术即 MMU,负责虚拟地址到物理地址的映射,并提供硬件机制的内存访问权限检查,通过使用 CACHE及 WRITE BUFFER技术缩小处理器和存储系统的差别,从而提高系统的整体性能

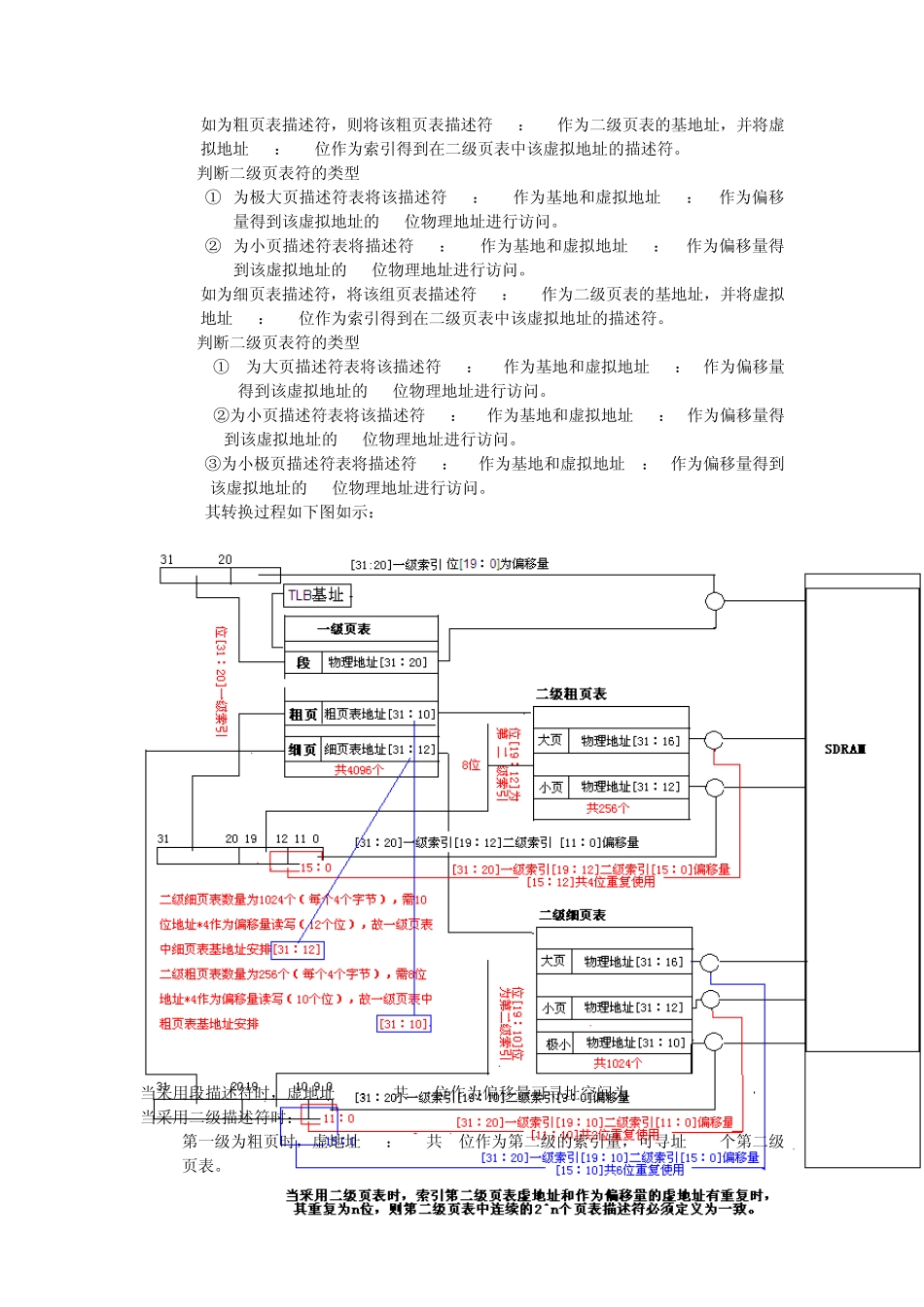

在系统加电时,将 ROM/FLASH映射为地址 0,进行一些初始化工作并将程序加载到 SDRAM中去,然后启用 MMU,将虚拟地址 0映射到 SDRAM地址(0x30000000),这样当中断产生时读取0x18处的指令时实际读取的是0x30000018处的指令,这样中断就就可以正确执行

S3c2440内存管理单元有如下特征: 4种映射长度,段1M、大页 64k、小页 4k,极小页 1k 指令 TLB(含 64个条目)、数据 TLB(含 64个条目) 硬件访问页表地址映射、权限检查由硬件自动完成 第一节 CP15寄存器的功能及读写 ARM的虚拟地址管理主要通过 CP15相关寄存器来实现的,CP15包括了 16个 32位寄存器,编号为 0~15,实际上对于某些编号的寄存器可能对应有多个物理寄存器,在指令编码时指定标志位来区分

CP15寄存器功能 编号 MMU功能 C0 ID编码(只读) C1 开启/禁止 MMU/CACHE/WRITE等功能 C2 地址转换表基地址 C3 域访问控制 C4 保留 C5 内存失效状态 C6 内存失效状态 C7 CACHE及 WRITE控制 C8 TLB控制 C9 CACHE锁定 C10 TLB锁定 C11 保留 C12 保留