锁相频率合成器实验设计 课程设计名称 指导老师 学生姓名 学生班级 同组人 锁相频率合成器实验设计 郑春来 王小慧 电子053 一、实验目的 了解锁相环的原理及应用 了解分频器的原理及应用 学会设计锁相频率合成器 二、实验器材 数字合成信号发生器SG1005、数字双踪示波器DS5062M 三、实验原理 锁相环电路是用于生成与输入信号相位同步的新的信号电路,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器

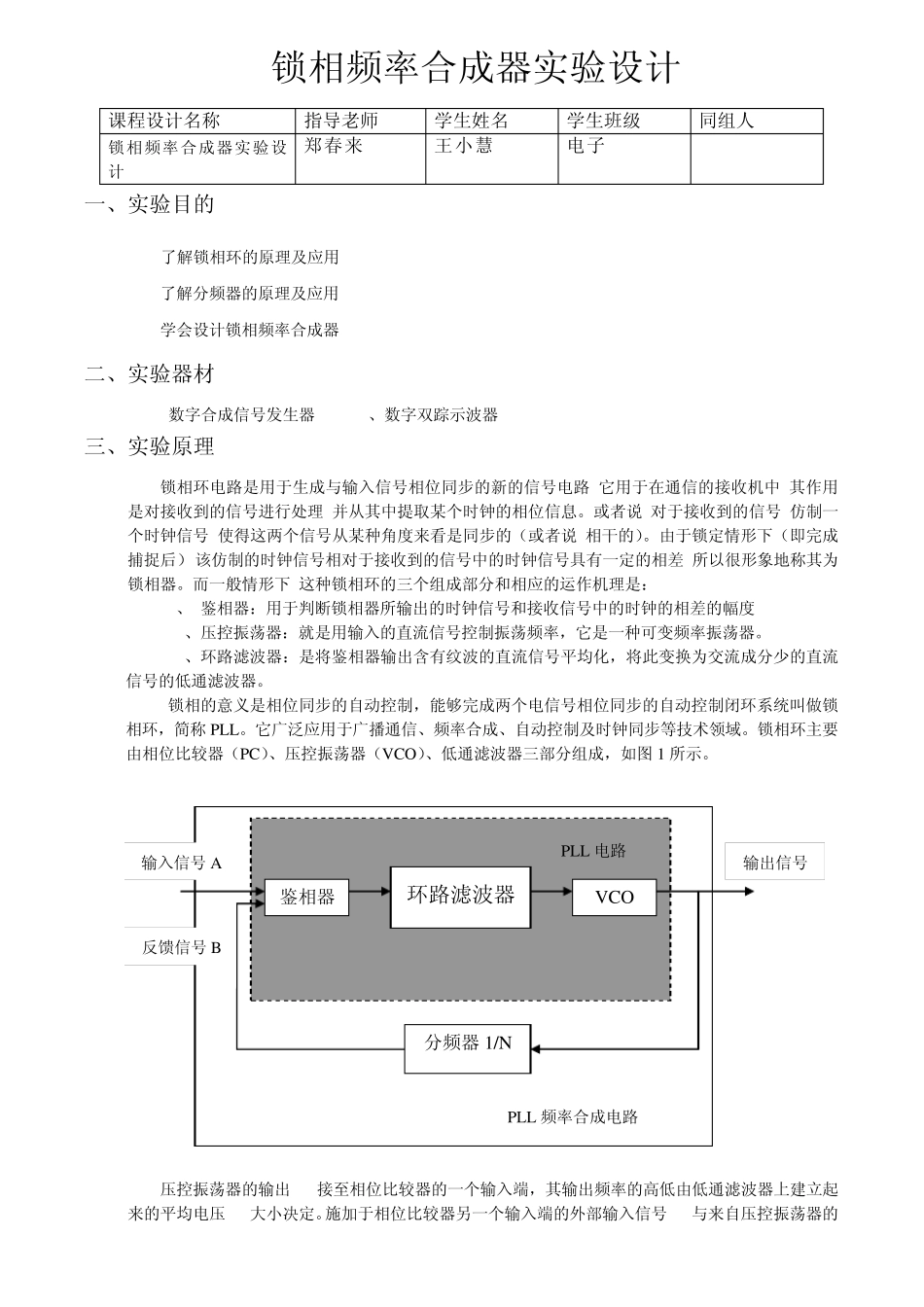

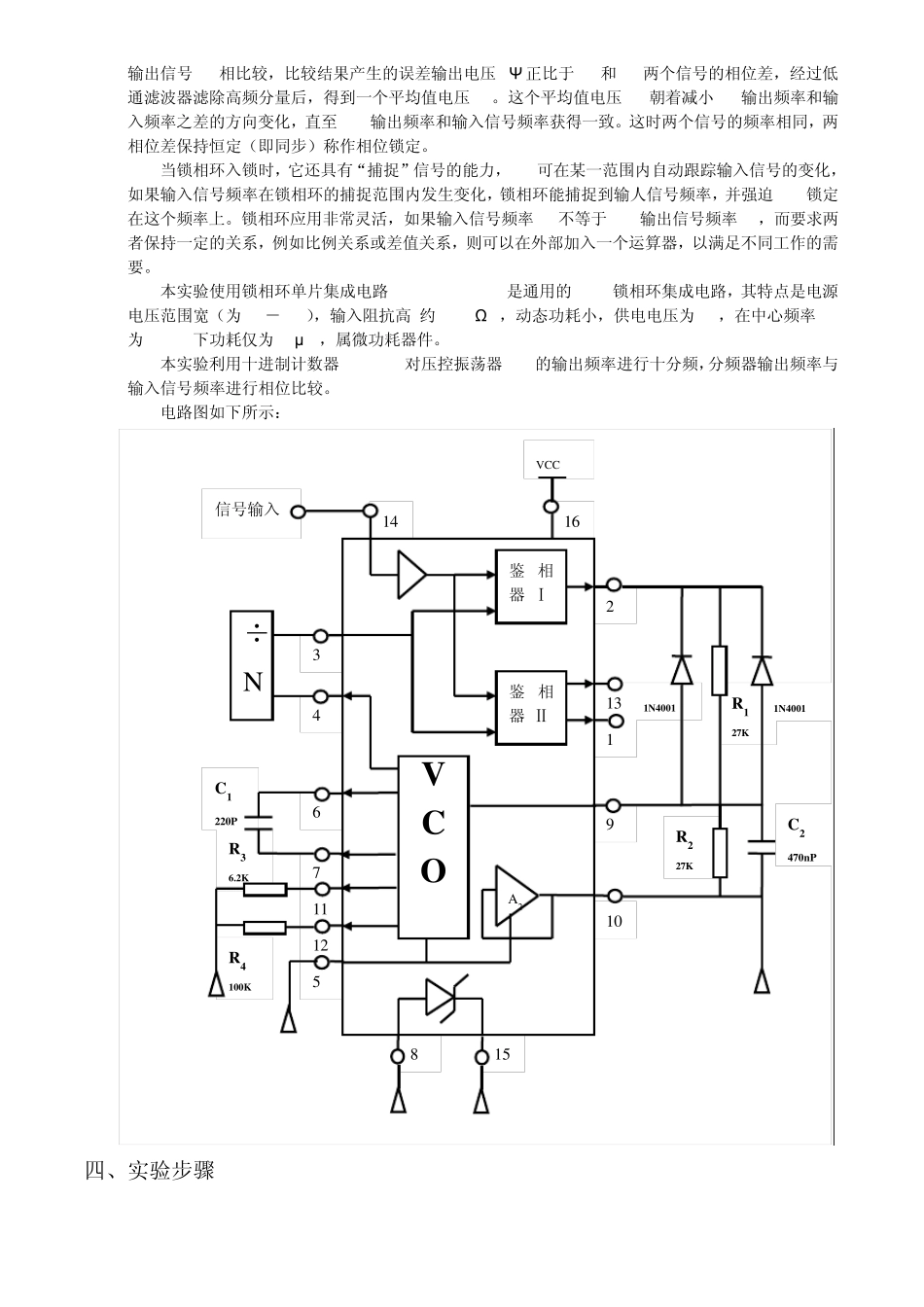

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是: 1、 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度; 2 、压控振荡器:就是用输入的直流信号控制振荡频率,它是一种可变频率振荡器

3 、环路滤波器:是将鉴相器输出含有纹波的直流信号平均化,将此变换为交流成分少的直流信号的低通滤波器

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域

锁相环主要由相位比较器(PC)、压控振荡器(V CO)、低通滤波器三部分组成,如图 1 所示

压控振荡器的输出 Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压 Ud大小决定

施加于相位比较器另一个输入端的外部输入信号 Ui与来自压控振荡器的鉴相器 环路滤波器 V CO 分频器1/N 反馈信号 B 输入信号 A 输出信号 PLL 电路 PLL 频率合成电路 输出信号 Uo相比较,比较结果产生的误差输出电压 UΨ 正