N 沟道金属氧化物半导体场效应晶体管(NMOSFET)工艺流程: 半导体元件制造过程可分为 前段(Front End)制造过程: 1

晶圆处理制程(Wafer Fabrication;简称 Wafer Fab) 2

晶圆针测制程(Wafer Probe); 后段(Back End): 1

构装(Packaging)、 2

测试制程(Initial Test and Final Test) 而本次课程设计主要重点在于前段晶圆的处理制作过程,故N 沟道金属氧化物半导体场效应晶体管(NMOSFET)工艺流程,概括的说就是先场氧,后栅氧,再淀多晶si,最后有源区注入

一.硅片的选取: 一般采用轻参杂的p型Si衬底,晶向,ρ=30~50Ω

晶圆(晶片)的生产由砂即(二氧化硅)开始,经由电弧炉的提炼还原成 冶炼级的硅,再经由盐酸氯化,产生三氯化硅,经蒸馏纯化后,透过慢速分解过程,制成棒状或粒状的「多晶硅」

一般晶圆制造厂,将多晶硅融解 后,再利用硅晶种慢慢拉出单晶硅晶棒

一支85 公分长,重76

6 公斤的 8 寸硅晶棒,约需 2 天半时间长成

经研磨、抛光、切片后,即成半导体之原料晶圆片 二

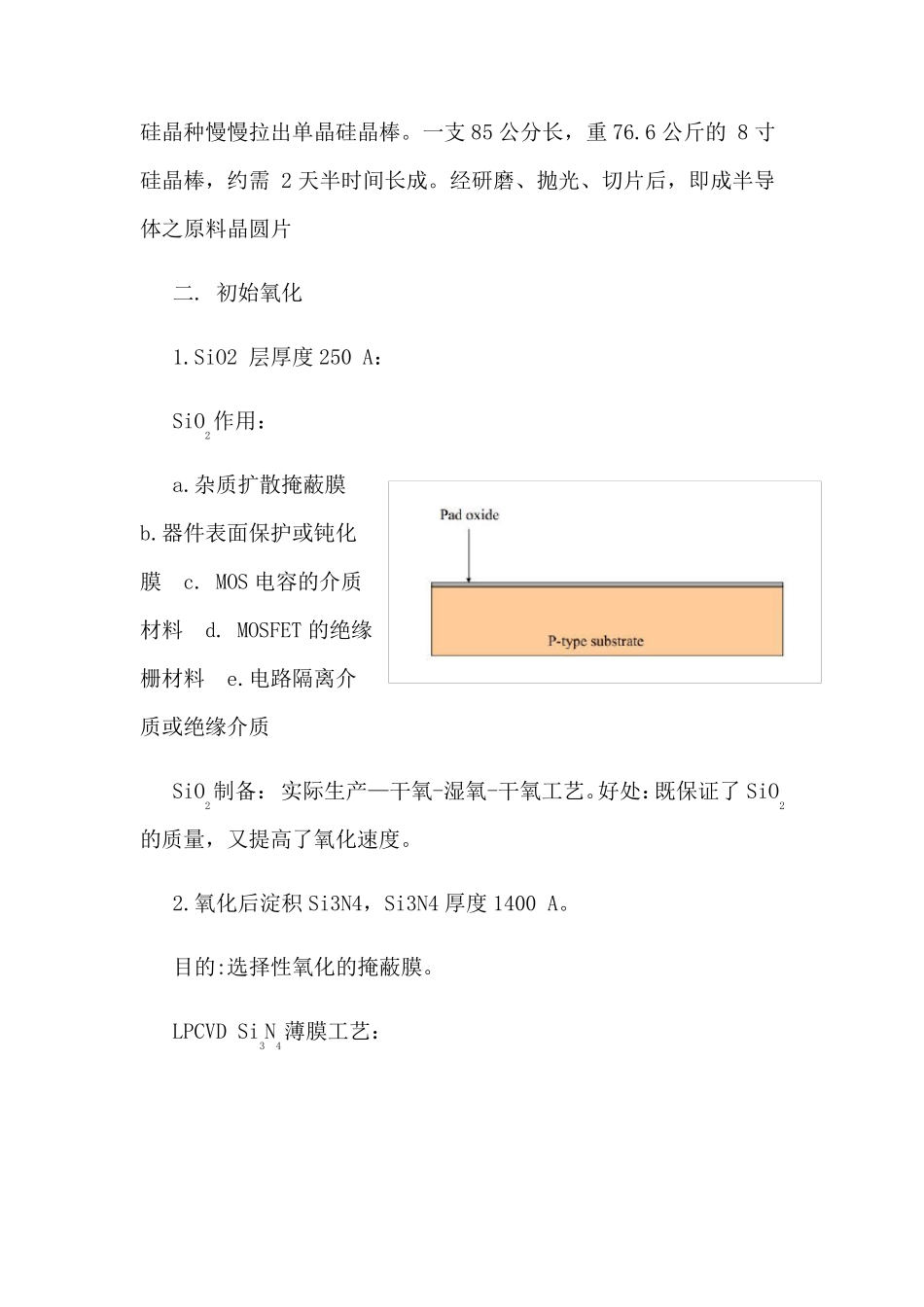

初始氧化 1

SiO2 层厚度250 A: SiO2作用: a

杂质扩散掩蔽膜 b

器件表面保护或钝化膜 c

MOS 电容的介质材料 d

MOSFET 的绝缘栅材料 e

电路隔离介质或绝缘介质 SiO2制备: 实际生产—干氧-湿氧-干氧工艺

好处:既保证了 SiO2的质量,又提高了氧化速度

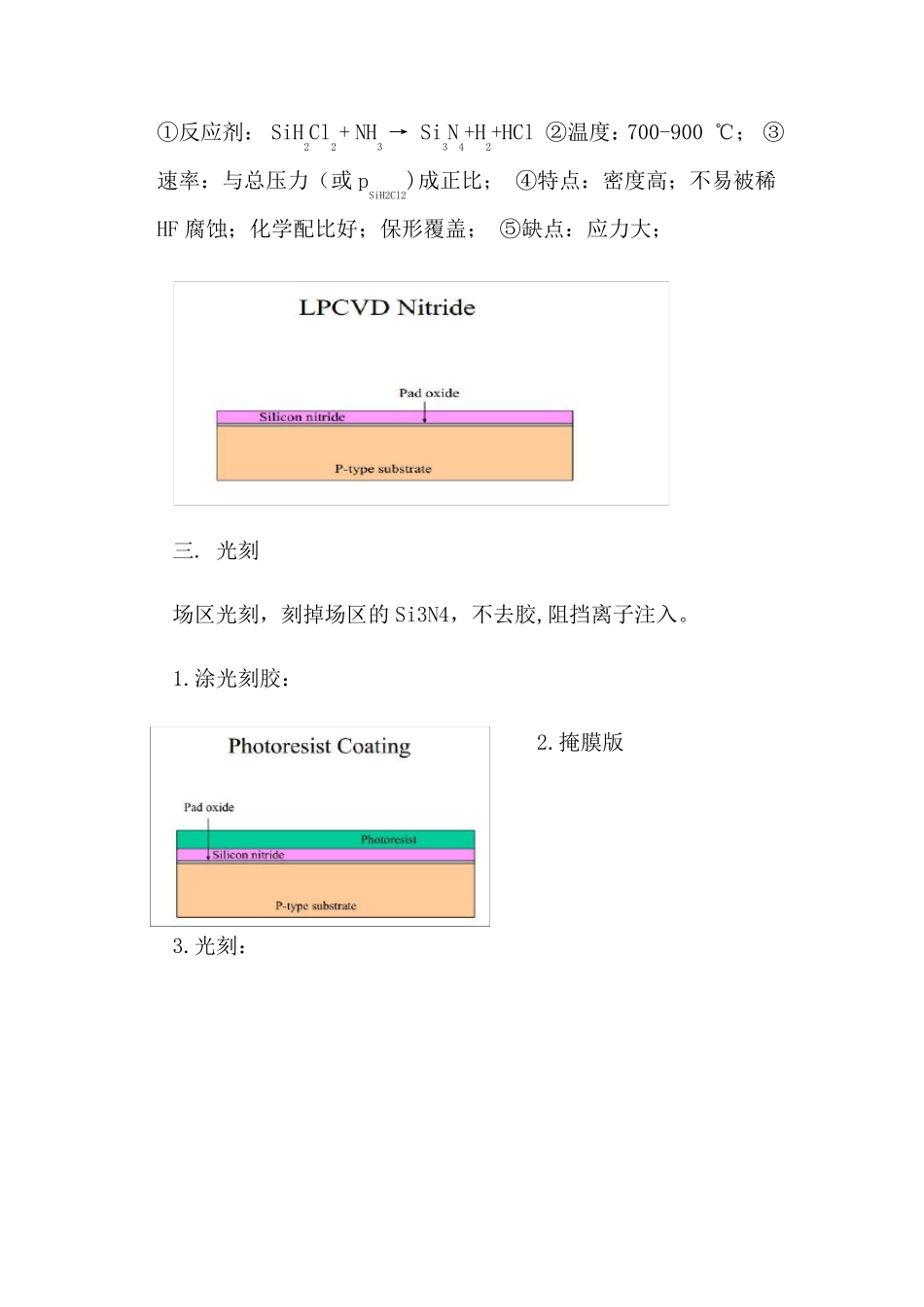

氧化后淀积 Si3N4,Si3N4 厚度1400 A

目的:选择性氧化的掩蔽膜

LPCVD Si3N4薄膜工艺: ①反应剂: SiH2Cl2 + NH3 → Si3N4+H2+HCl ②温度:700-900 ℃; ③速率:与总压力(或 pSiH2Cl2)成正比; ④特点:密度高;不易