下载后可任意编辑Verilog 实验报告实验一 Quartus 及 Modelsim 软件的基本使用一、实验目的熟悉 Quartus 和 Modelsim 软件的基本使用方法和步骤,熟悉基本的 Verilog 语法,学会用 Verilog 语言编写简单的程序

二、实验要求熟练掌握 Quartus 和 Modelsim 软件工程建立、添加文件、编译运行和仿真的方法,学会写程序文件和测试文件

三、实验仪器和设备1、硬件:计算机2、软件:Quartus、Modelsim、(UE)四、实验内容1、运行 Quartus 软件建立工程并添加程序

v 文件,编译运行,查看电路图

2、运行 Modelsim 软件建立工程并添加测试

v 文件,进行仿真,查看波形图

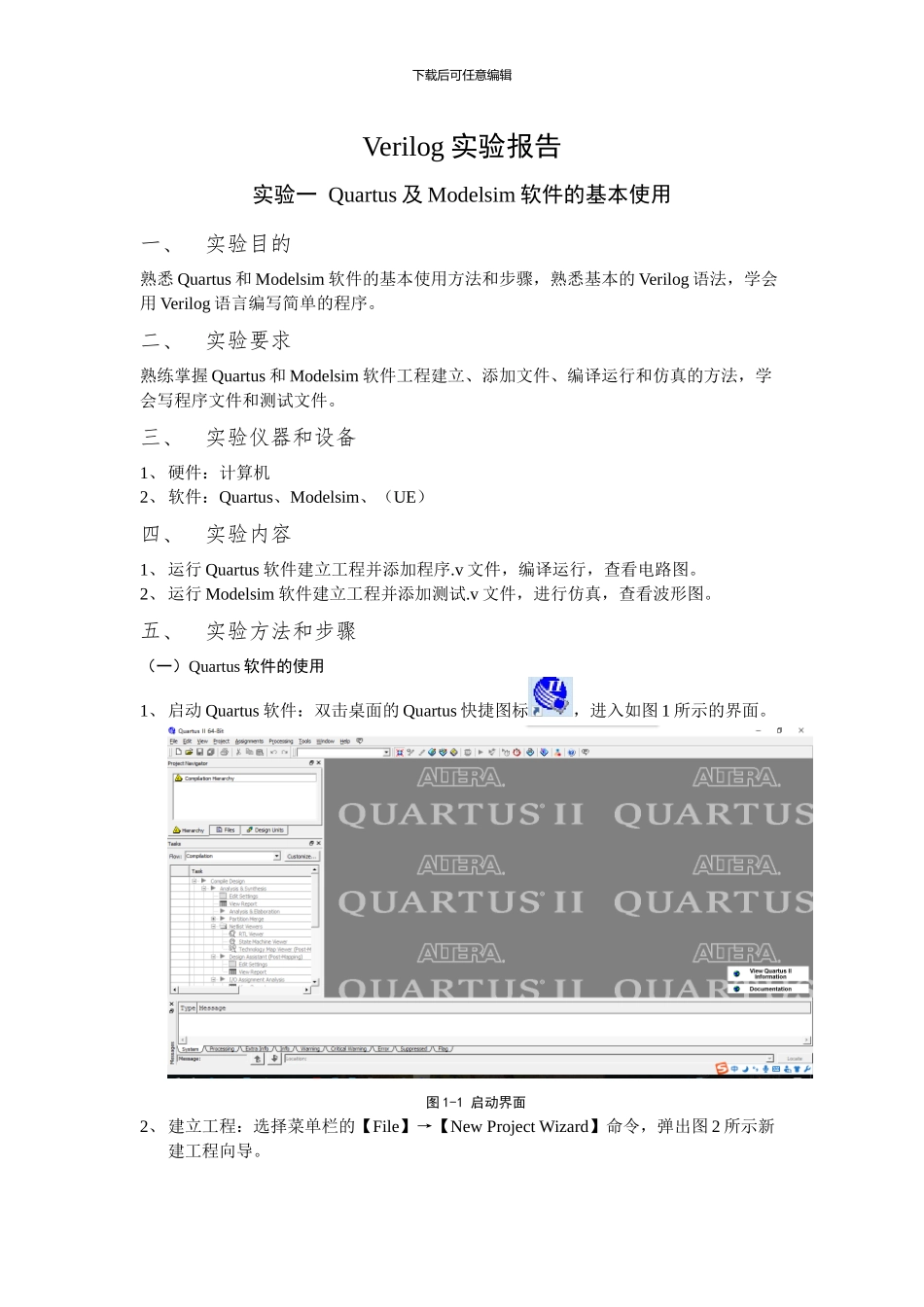

五、实验方法和步骤(一)Quartus 软件的使用1、启动 Quartus 软件:双击桌面的 Quartus 快捷图标,进入如图 1 所示的界面

图 1-1 启动界面2、建立工程:选择菜单栏的【File】→【New Project Wizard】命令,弹出图 2 所示新建工程向导

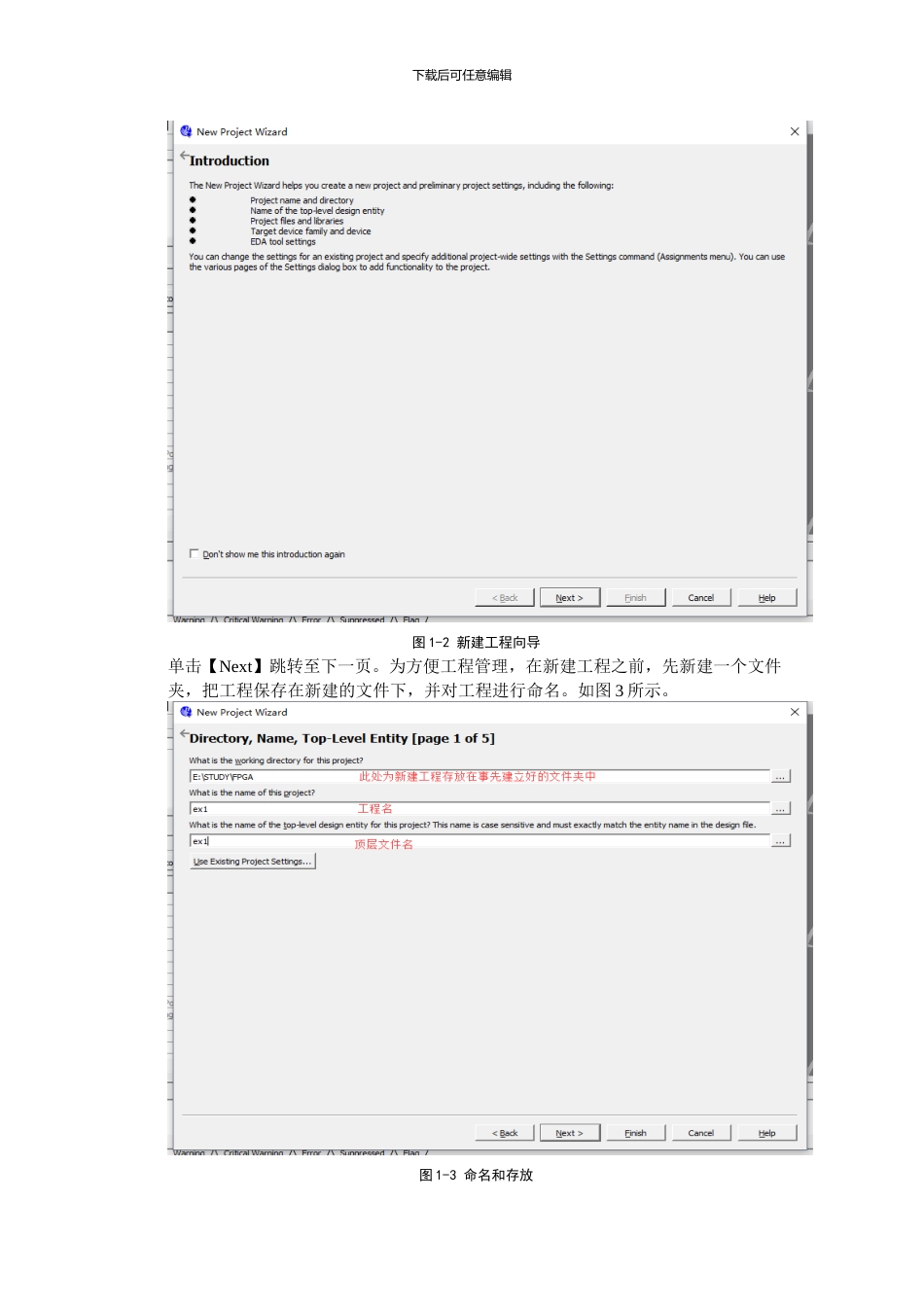

下载后可任意编辑图 1-2 新建工程向导单击【Next】跳转至下一页

为方便工程管理,在新建工程之前,先新建一个文件夹,把工程保存在新建的文件下,并对工程进行命名

如图 3 所示

图 1-3 命名和存放下载后可任意编辑单击【Next】跳转至下一页

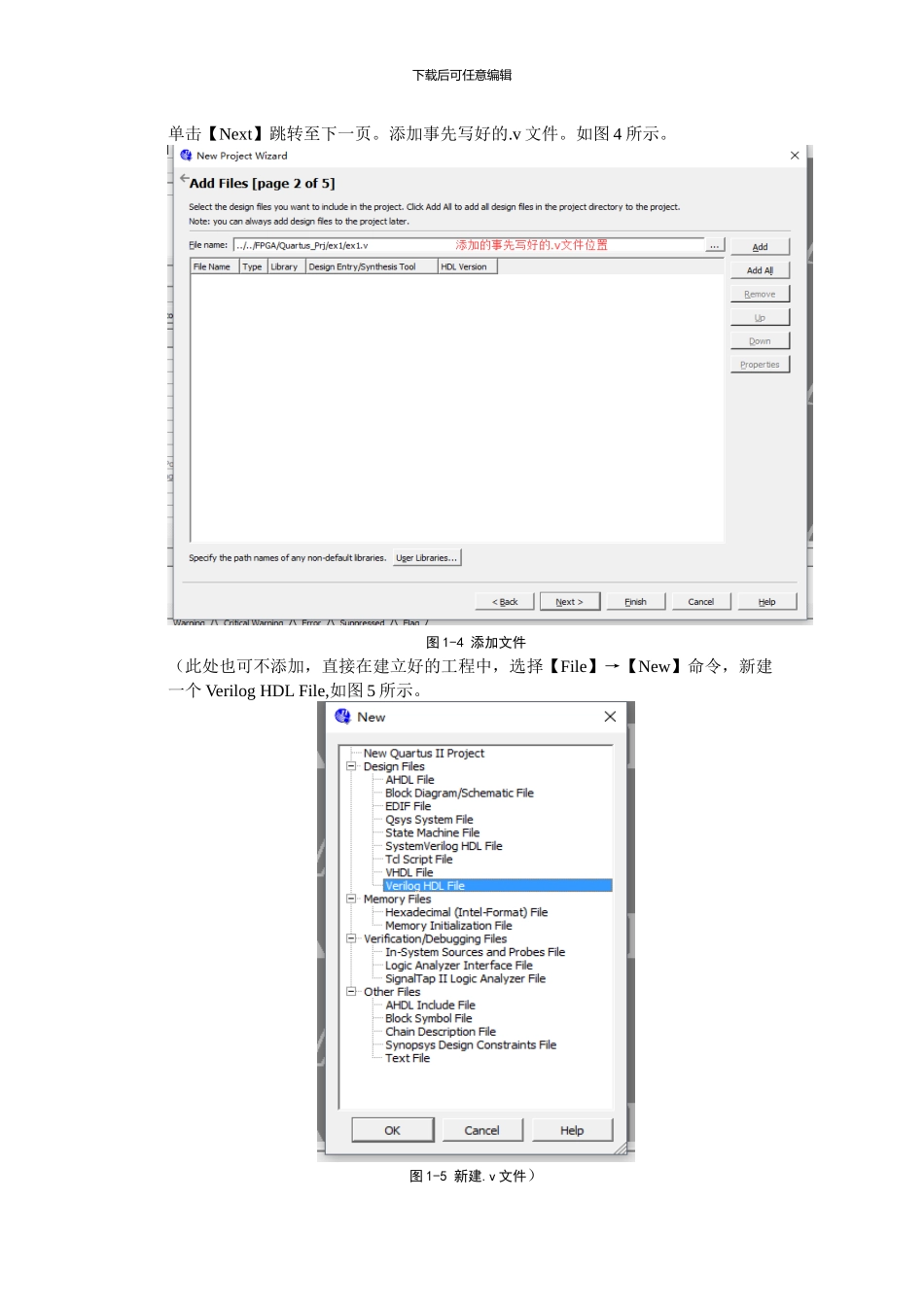

添加事先写好的

如图 4 所示

图 1-4 添加文件(此处也可不添加,直接在建立好的工程中,选择【File】→【New】命令,新建一个 Verilog HDL File,如图 5 所示

图 1-5 新建

v 文件)下载后可任意编辑单击【Next】跳转至下一页

选择 FPGA 型号,如图 6 所示

因为本次实验不在硬件上实现,因此此步跳过

直接单击【Next】跳转至下一页

图 1-6 选择 FPGA 型