Cyclone 系列FPGA 具有锁相环(PLL)和全局时钟网络,PLL 具有时钟的倍频、分频、相位偏移、可编程占空比和外部时钟输出

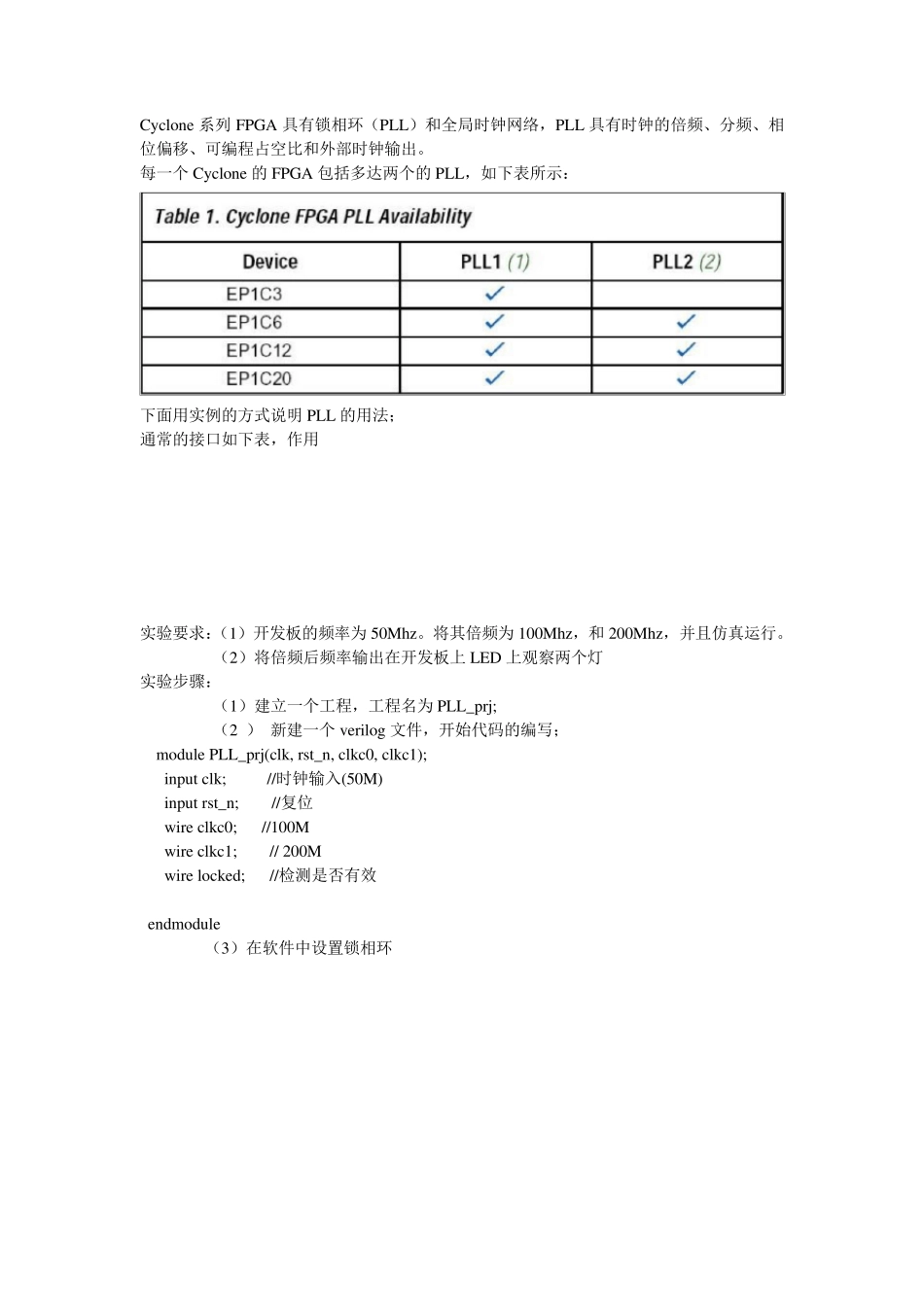

每一个 Cyclone 的FPGA 包括多达两个的PLL,如下表所示: 下面用实例的方式说明 PLL 的用法; 通常的接口如下表,作用 实验要求:(1)开发板的频率为 50Mhz

将其倍频为 100Mhz,和200Mhz,并且仿真运行

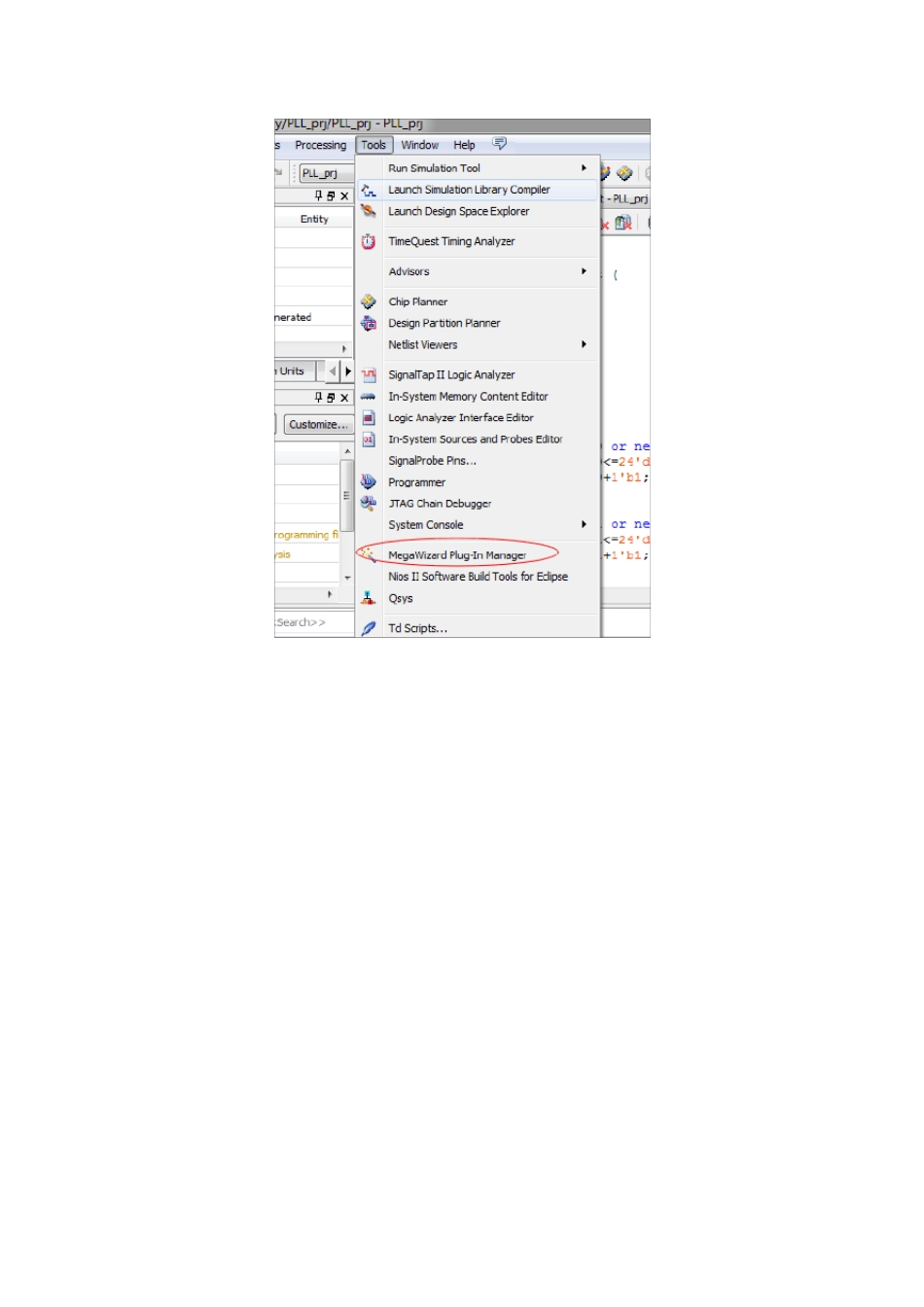

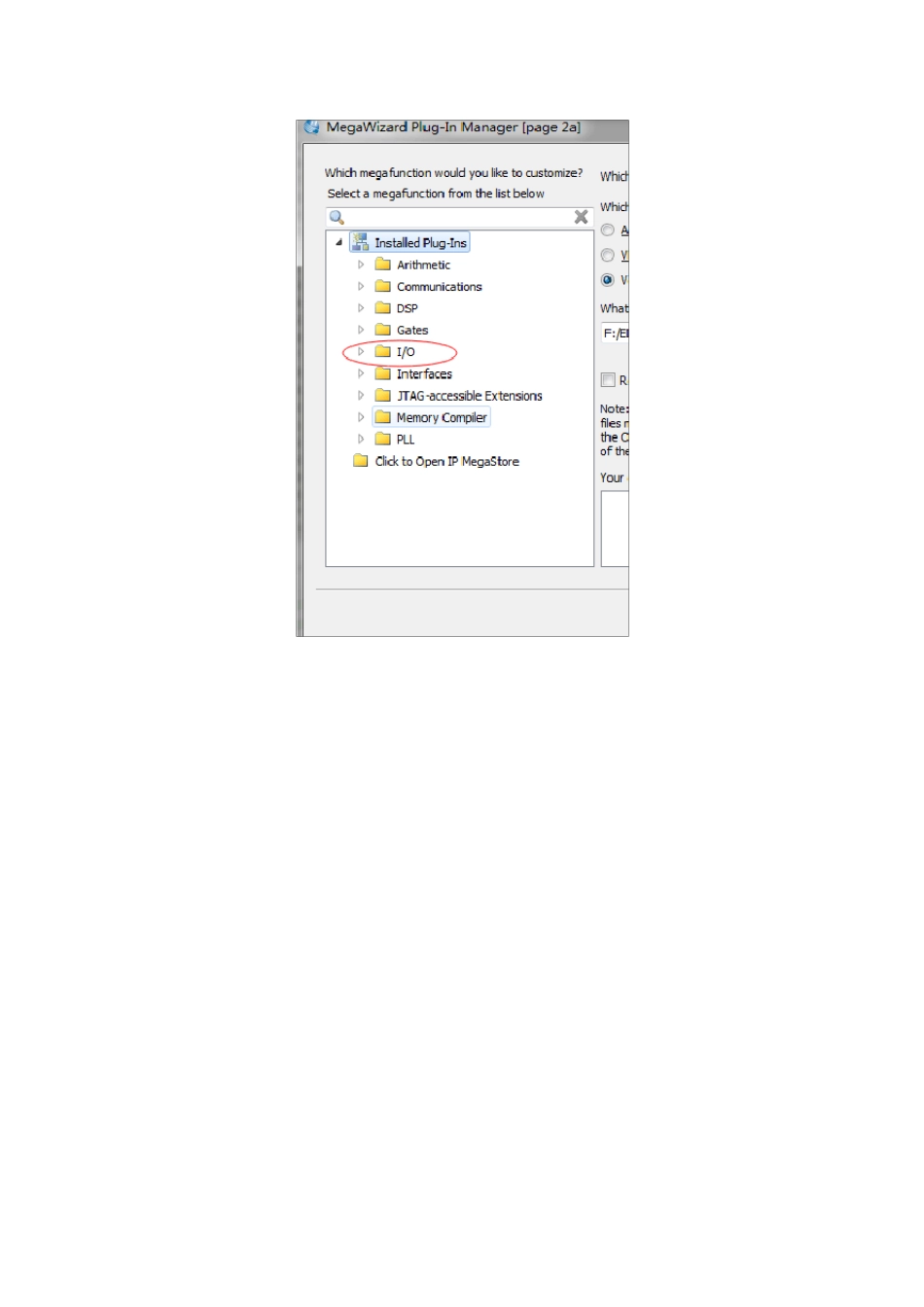

(2)将倍频后频率输出在开发板上 LED 上观察两个灯 实验步骤: (1)建立一个工程,工程名为 PLL_prj; (2 ) 新建一个 verilog 文件,开始代码的编写; module PLL_prj(clk, rst_n, clkc0, clkc1); input clk; //时钟输入(50M) input rst_n; //复位 wire clkc0; //100M wire clkc1; // 200M wire locked; //检测是否有效 endmodule (3)在软件中设置锁相环 之后就会弹出来如下图所示页面 上边有5 个选项卡(不同版本可能有点差别) 第一个里面如下 创建上面说到复位和检测 第二页默认就可以了 第三页 不同的器件能够建立输出个数也不一样这里我们用前俩个 一些文件的输出 配置完成之后 到这个时候就已经在软件中配置好了 PLL 接下来就是列化了 打开文件复制里面的代码到刚开始建立的

v 文件中 修改补充完全代码如下: module PLL_prj( clk, rst_n, led0, led1 ); input clk; //50M input rst_n; //rest output led0; output led1; wire clkc0; //100M wire clkc1; //200M wire locked; PLL_ctrl PLL_ctrl_inst