ISE 整体开发流程:建工程→编写工程代码→检查语法错误→行为仿真→综合→管脚约束→实现→时序仿真→生成 bit 流文件→下载到板子上调试; 实验是用 ISE10

1 做的,与 ISE9

1 不同的地方在文中也有相关说明

一:建工程 1

工程命名 file→new projiect(如下图所示:在工程名处填:jishuqi 资源类型选:HDL) 2

器件类型选择及仿真综合工具、硬件描述语言设置 点击 Next,出现如下图所示界面: 图中设置的有:Family:virtex2P; Device :XC2VP30;Package:FF896;Speed:-7(这个是根据VIRTEX2P 开发板设置的数据,不同的开发板设置的数据不一样)

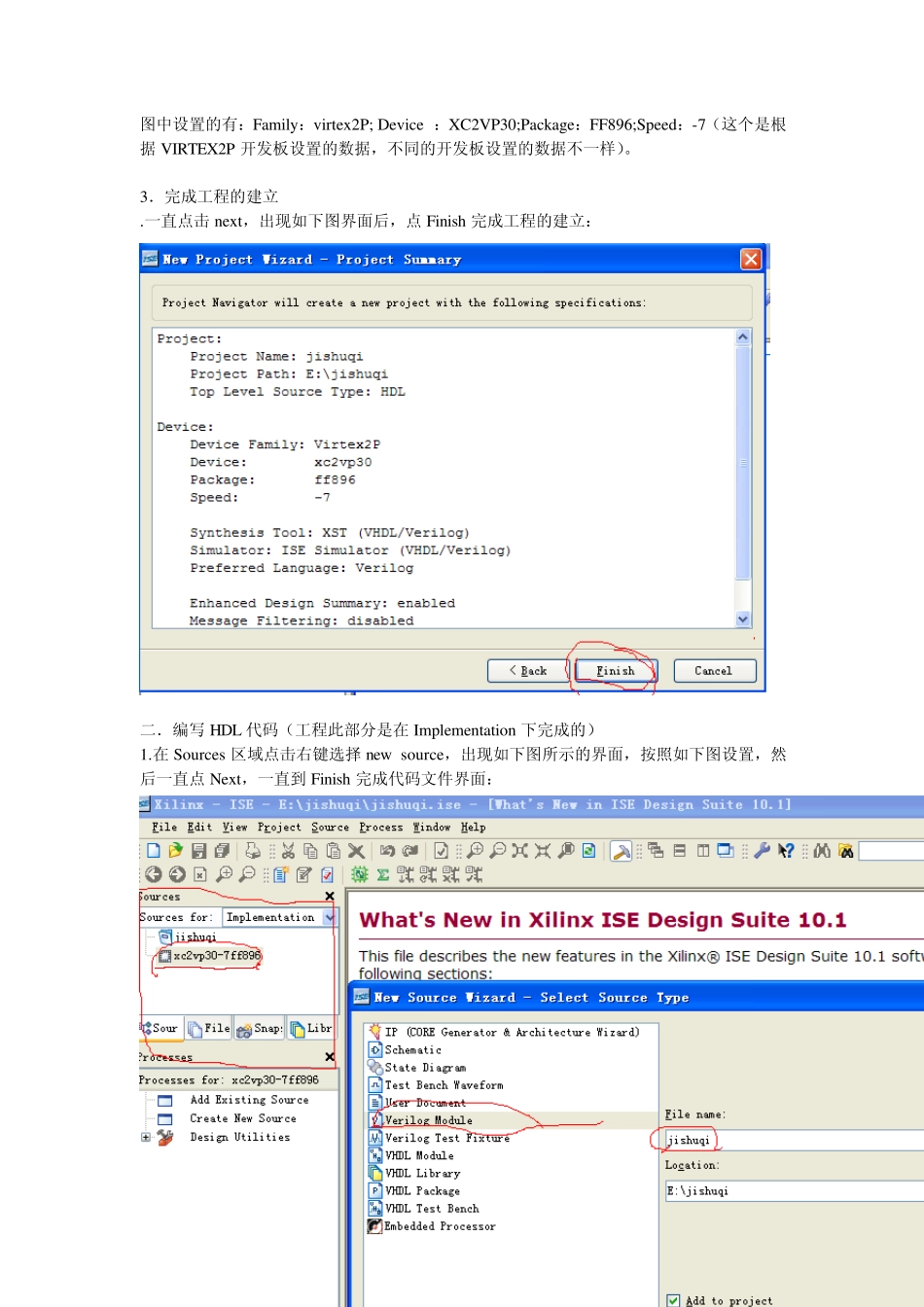

3.完成工程的建立

一直点击 next,出现如下图界面后,点 Finish 完成工程的建立: 二.编写 HDL 代码(工程此部分是在 Implementation 下完成的) 1

在 Sources 区域点击右键选择 new source,出现如下图所示的界面,按照如下图设置,然后一直点 Next,一直到 Finish 完成代码文件界面: 3

接下来开始HDL 代码编写,这里是一个简单的十进制计数器的编写: 代码编写好后,点击保存,然后检查看编写代码是否有错误,如上图所示,Check Syntax 点击检查后是绿色的勾,则代码没有语法错误,可以进行下一步功能仿真; module jishuqi(clk,rst,q); input clk,rst; output[3:0] q; reg[3:0] q; always@(posedge clk) begin if(rst==0) q