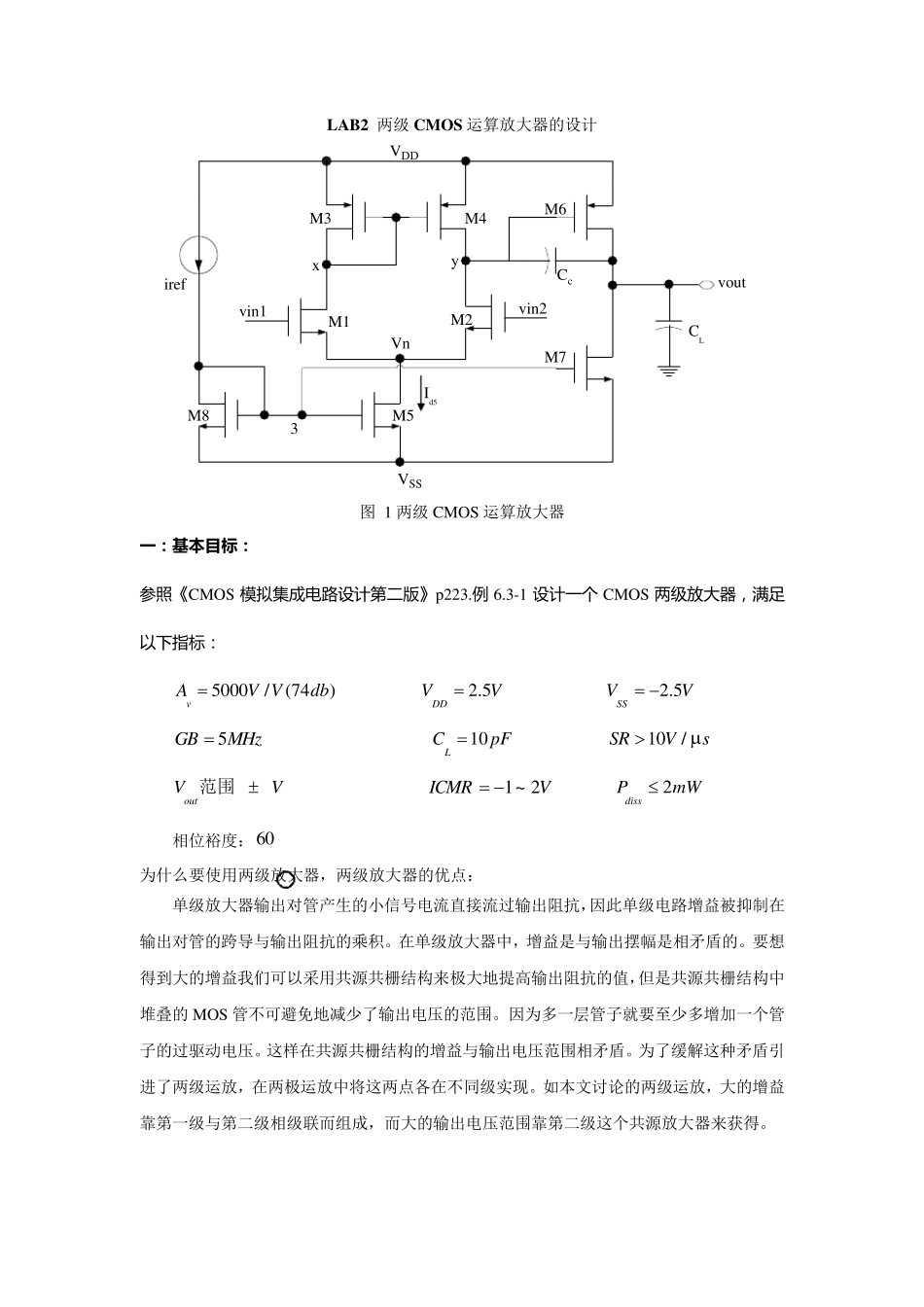

LAB2 两级CMOS运算放大器的设计 VDDVSSM1M2M3M4M5M6M7M8VnCLCcvoutvin1vin2irefxy3 Id5 图 1 两级CMOS 运算放大器 一:基本目标: 参 照 《CMOS 模拟集成电路设计第二版》p223

3-1 设计一个 CMOS 两级放大器,满足以下指标: 5000/(74)vAV Vdb 2

5DDVV 2

5SSVV 5GBMHz 10LCpF 10/SRVs outVV范围= 2 1~ 2ICMRV 2dissPmW 相位裕度:60 为什么要使用两级放大器,两级放大器的优点: 单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积

在单级放大器中,增益是与输出摆幅是相矛盾的

要想得到大的增益我们可以采用共源共栅结构来极大地提高输出阻抗的值,但是共源共栅结构中堆叠的MOS 管不可避免地减少了输出电压的范围

因为多一层管子就要至少多增加一个管子的过驱动电压

这样在共源共栅结构的增益与输出电压范围相矛盾

为了缓解这种矛盾引进了两级运放,在两极运放中将这两点各在不同级实现

如本文讨论的两级运放,大的增益靠第一级与第二级相级联而组成,而大的输出电压范围靠第二级这个共源放大器来获得

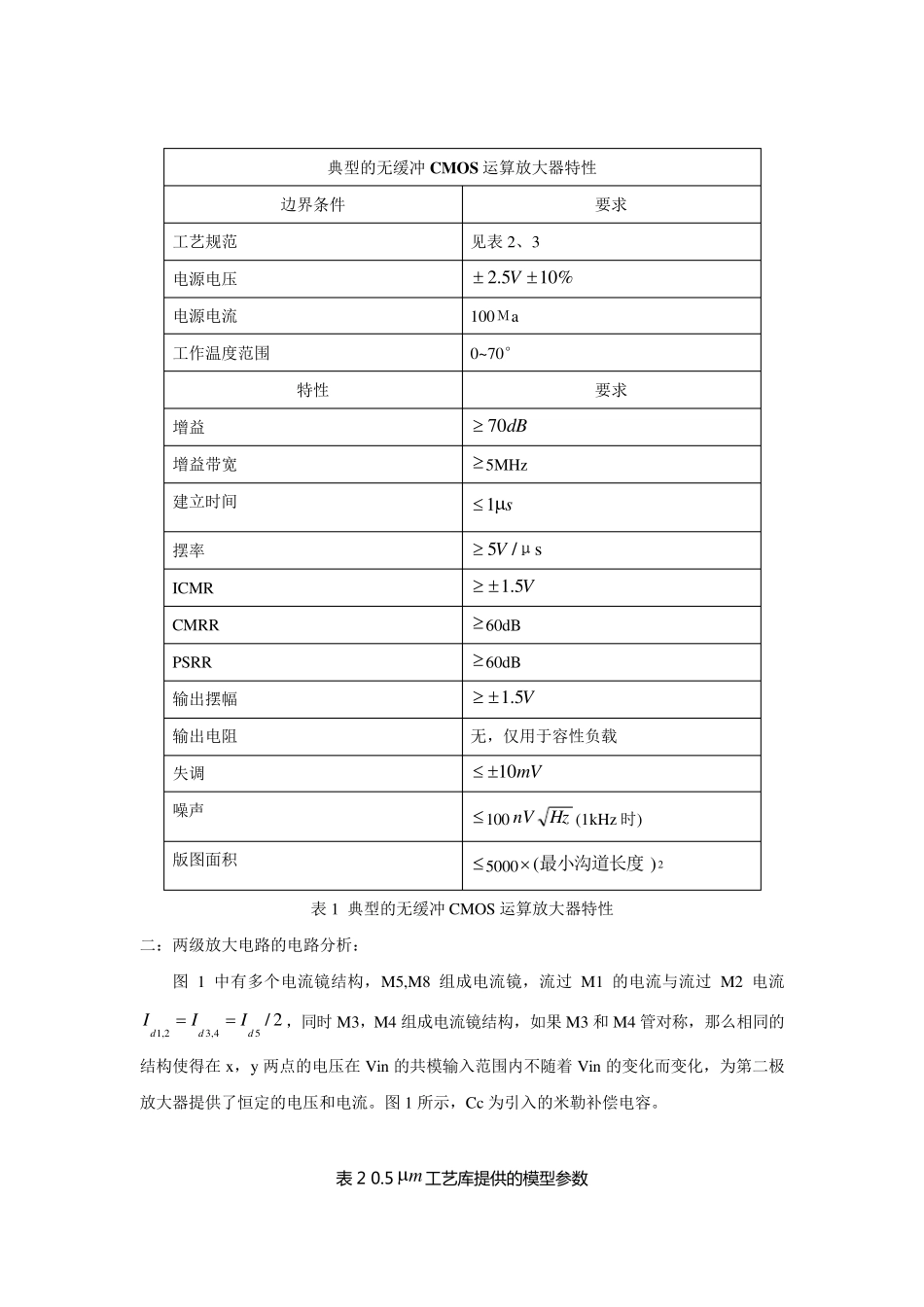

典型的无缓冲CMOS运算放大器特性 边界条件 要求 工艺规范 见表2、3 电源电压 %105

2V 电源电流 100Μa 工作温度范围 0~70° 特性 要求 增益 dB70 增益带宽 5MHz 建立时间 s1 摆率 s/5μV ICMR V5

1 CMRR 60dB PSRR 60dB 输出摆幅 V5

1 输出电阻 无,仅用于容性负载 失调 mV10 噪声 100HznV(1kHz 时) 版图面积 50002)(最小沟道长度 表1