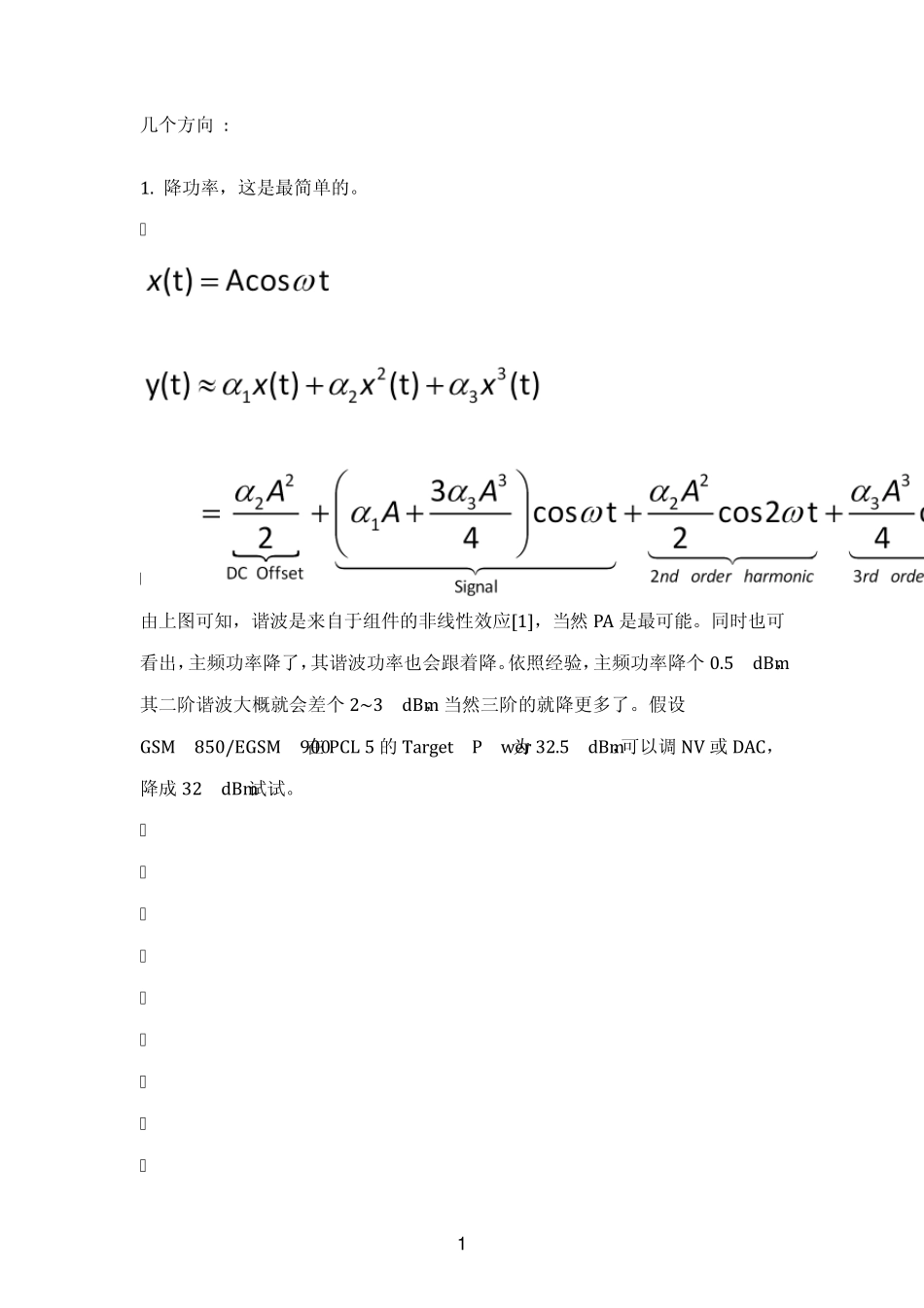

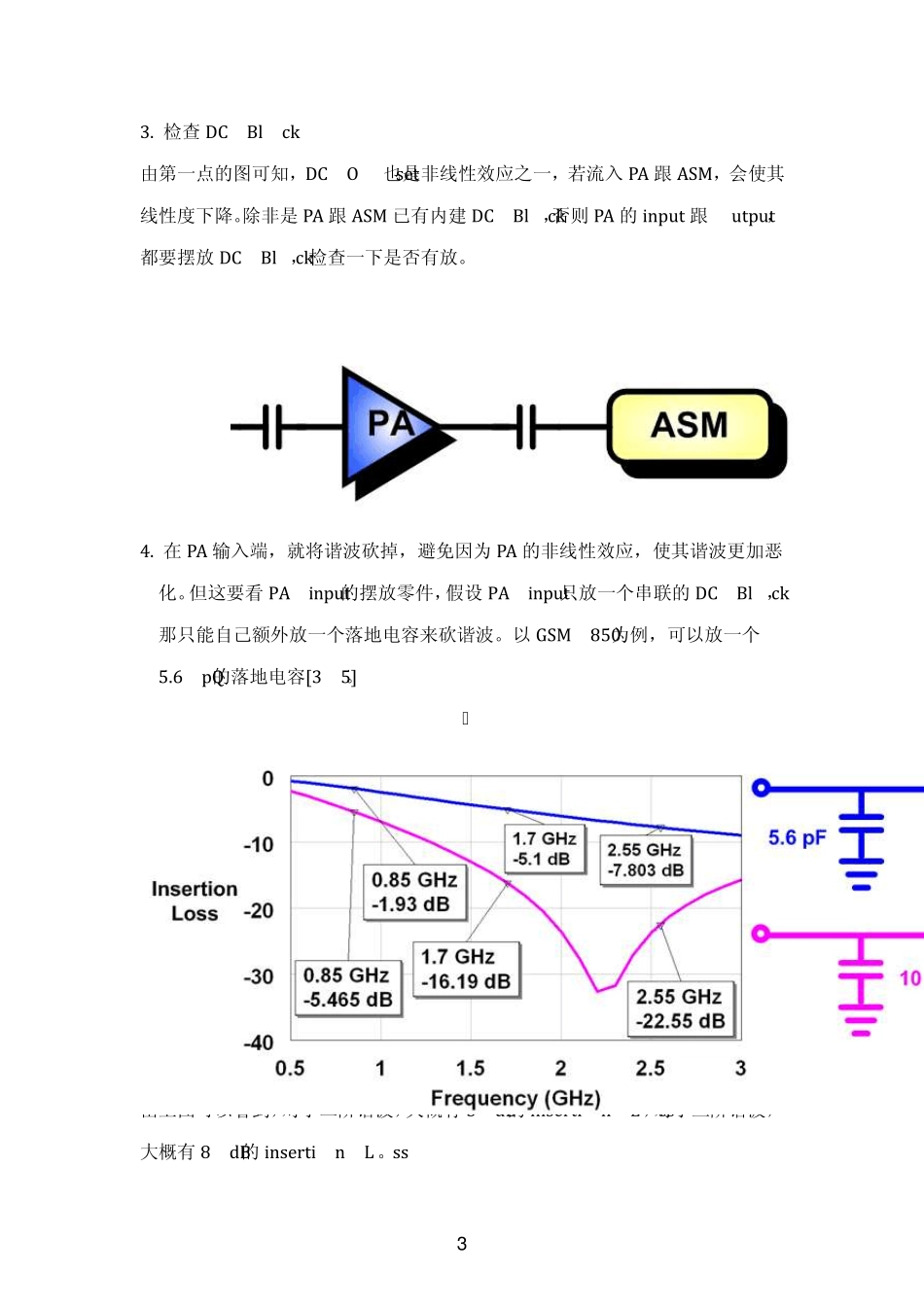

几个方向 : 1. 降功率,这是最简单的。 由上图可知,谐波是来自于组件的非线性效应[1],当然 PA 是最可能。同时也可看出,主频功率降了,其谐波功率也会跟着降。依照经验,主频功率降个0.5 dBm,其二阶谐波大概就会差个2~3 dBm,当然三阶的就降更多了。假设 GSM 850/EGSM 900在 PCL 5 的Target Power为 32.5 dBm,可以调 NV 或 DAC, 降成 32 dBm试试。 12. 若是高通平台,可以调NV。下图是PA_Enable、ANT_SEL、V_ramp 三条曲线 。 这三条曲线,对于谐波以及开关频谱,都会有影响,建议 PA_Enable 比 V_ramp早开启,而且最好能早一段时间。而 Ant_sel 可以比 PA_en 早开启,也可以比 PA_en晚开启,看怎样的 NV 值, 其谐波以及开关频谱会最低[2] 。 23. 检查DC Block 由第一点的图可知,DC Offset也是非线性效应之一,若流入PA 跟ASM,会使其线性度下降。除非是PA 跟ASM 已有内建 DC Block,否则 PA 的inpu t 跟ou tpu t, 都要摆放 DC Block,检查一下是否有放。 4. 在 PA 输入端,就将谐波砍掉,避免因为 PA 的非线性效应,使其谐波更加恶化。但这要看 PA inpu t的摆放零件,假设 PA inpu t只放一个串联的DC Block, 那只能自己额外放一个落地电容来砍谐波。以 GSM 850为例,可以放一个 5.6 pF的落地电容[3-5]。 由上图可以看到,对于二阶谐波,大概有 5 dB的insertion Loss,对于三阶谐波, 大概有 8 dB的insertion Loss。 3特别注意的是,在设计电容值时,不是谐波抑制能力越大越好,因为一般普通的COG 电容,其频率响应,不会只砍到谐波,同时也会砍到主频。假设放 10 pF的落地电容,可以看到二阶谐波,大概有 16 dB的insertion Loss。三阶谐波,大概有 22 dB的insertion Loss。但主频也被砍了 5 dB。另外落地电容会使阻抗偏掉,如下图[6] : 换句话说,会有 Mismatch Loss,在这情况下,10pF 的落地电容,其insertion Loss跟 Mismatch Loss加一加,可能会使主频的讯号过低,甚至低于 PA 输入范围的下限。同时我们也看到,虽然三阶谐波的抑制能力更好,但三阶谐波的频率,已座落在谐振频率的右边。换言之,此时是利用该落地电容的电感性去砍三阶谐波,如下图[3-5] : 4 把电容当电感用,某种程度上会有一些未知的风险,最好是极力避免。 而前述的5.6 pF落地电容,其二三阶谐波都座落在谐振频率的左边,同时主频只被砍了 2 ...