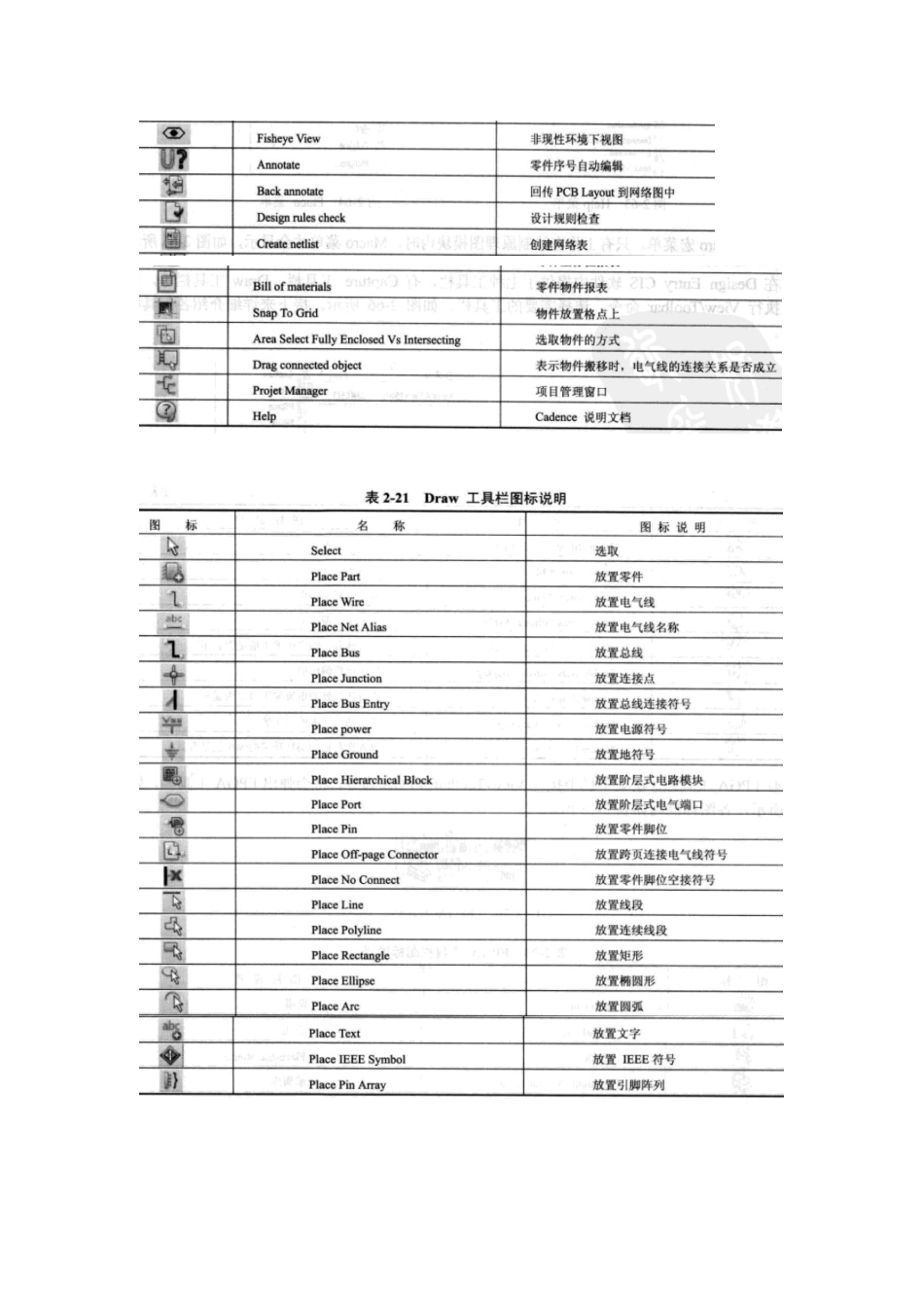

Cadence 原理图设计技巧一、工具栏介绍二、原理图设计规三、原理图设计基本步骤生成文件网表用于制作 PCB 文件 元器件明细用于制作明细表 元器件清单用于器件采购 Tcl 文件用于导入 Quartus II 进行 FPGA 管脚验证个人经验:生成的文件以 pdf 格式打印出来(包括原理图),更加方便使用四、常用操作(1) 元器件镜像翻转: 选中后 Edit/Mirror/Horizontally (水平) /Vertically (垂直)(2) Edit text 容换行:Ctrl+Enter(3) 元器件批量修改:选中所需修改的元器件,右键 Edit Properties(4) 在管脚标示上加横线 Eg:1OE—》1O\E\ 回车(5) 元件库中填充:选中闭环的图形,右键选中 Edit Properties File style 下拉列表选中 Soild常用快捷键 -1

放大/缩小—— I/O 或 Ctrl+滚轮上/下2

放置元器件—— P3

放置地—— G4

元器件旋转 ——R5

放置 wire—— W6

放置 Net—— N7

放置 Text—— T五、基本技巧1

Find 功能使用然后点击工程 dsn 文件,Ctrl+F 调出查找Match Case:大小写匹配Highlight :高亮显示所查网络/器件2

生成元器件清单选中 DSN 文件,Tools/Bill of Materials3

如何检查原理图错误(1)查看原理图中的元器件信息如下图(2)查看网络信息双击某一网络即可查看其在原理图中的位置,进而检查原理图错误(3)DRC 检查选中工程 DSN 文件,Tools/Design Rules Check4

从原理图中导出网表设置完毕之后,会在指定路径下产生 pstchip

dat,pstxnet

dat,patxprt

dat 文件pstchi