匚卩—电学实验报告模板电学虚拟仿真实验室实验名称触发器:测试 74LS112(双 JK 触发器)-元件实验目的1

掌握边沿触发器的逻辑功能

掌握边沿触发器逻辑功能测试方法

触发器的触发方式(1)电平触发方式电平触发方式的特点是:厂二】时,输出与输入之间通道“透明”,输入信号的任何变化都能引起输出状态的变化

当二二时,输入信号被封锁,输出不受输入影响,保持不变

(2)边沿触发方式边沿触发方式的特点是:仅在时钟 CP 信号的上升沿或下降沿才对输入信号响应

触发器的次态仅取决于时钟 CP 信号的上升沿或下降沿到达时输入端的逻辑状态,而在这以前或以后,输入信号的变化对触发器输出端状态没有影响

边沿 JK 触发器图 1 下升沿触发 JK 触发器逻辑符号图 1 所示为下降沿触发 JK 触发器的逻辑符号

下降沿 JK 触发器的特性表如表 1所示

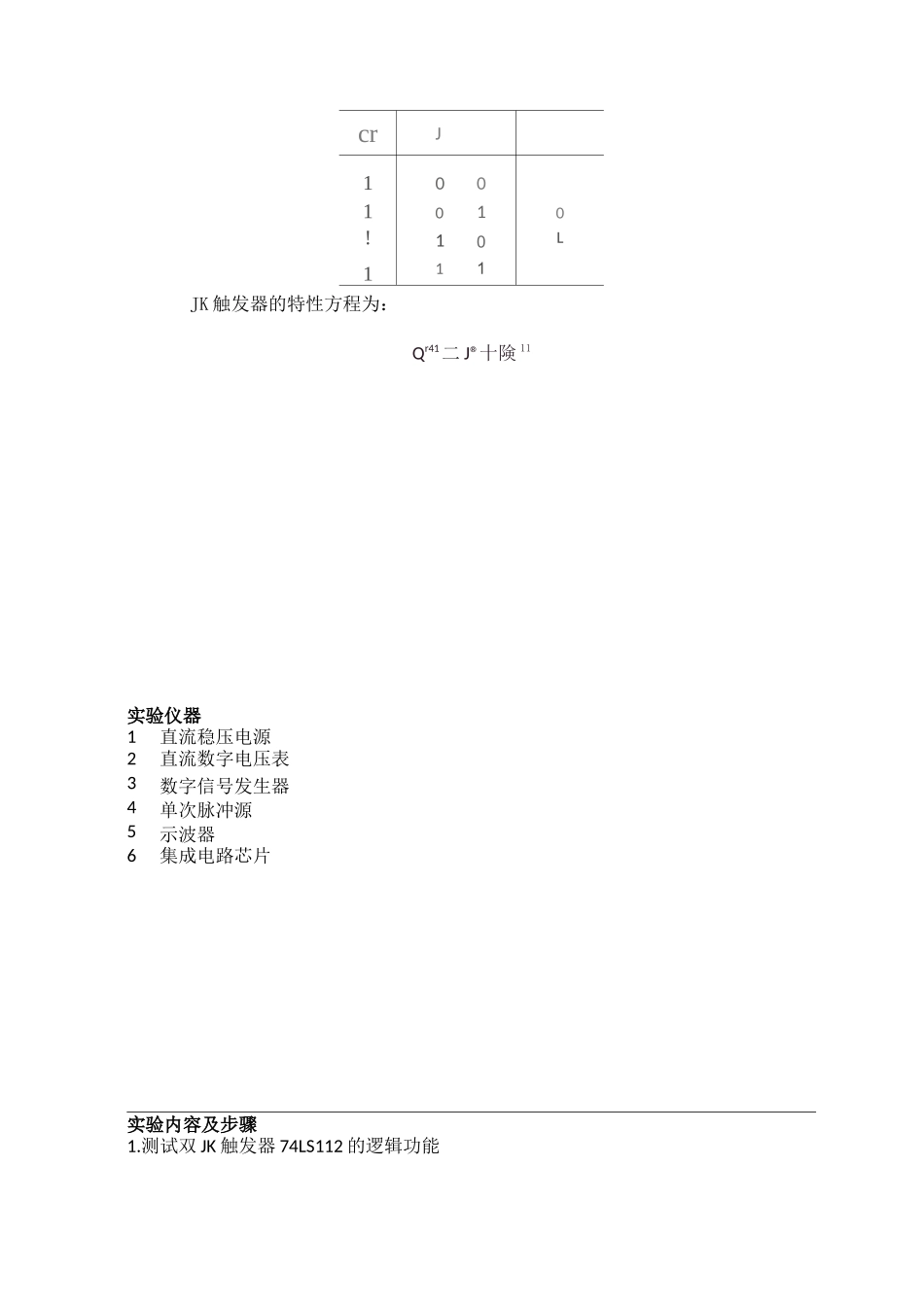

表 1 下降沿 JK 触发器特性表crJ1001010

10L111JK 触发器的特性方程为:Qr41二 J®十険 11实验仪器1直流稳压电源2

直流数字电压表3

数字信号发生器4

单次脉冲源5

示波器6集成电路芯片74LS112实验内容及步骤1

测试双 JK 触发器 74LS112 的逻辑功能(1)74LS112 引脚图VLX-图 274LS112 引脚图图 2 所示为集成电路芯片 74LS112 的引脚图

芯片包含两个带有异步置位复位端的下降沿 JK 触发器

(2)测试 74LS112 的逻辑功能图 3 测试 74LS112 的逻辑功能实验电路按照图 3 连接电路

JK 触发器的 Q 和二(芯片 5 和 6 号引脚)各接一个发光二极管用以观察触发器的输出逻辑电平

第 1 步:置…:汽」则 Q=J=1 和 K=1-置,CP 输入单次脉冲,Q 和 Q 不变

改变 J 或 K,再次使 CP 输入单次脉冲,Q 和 4 仍不