锁相频率合成器的设计设计任务和技术指标1

工作频率范围:300kHz—700kHz2

电源电压:Vcc=5V3

通过原理图确定电路,并画出电路图,计算元件参数选取电路元件(R1,R2,C1,R1ˊ,R2ˊ 及环路滤波器的配置)4

组装连接电路,并测试选取元件的正确性,调试并测量电路相关参数(测量相关频率点,输出波形,频率转换时间 tc)5

总结并撰写实验报告设计方案锁相频率合成器原理锁相环(PLL)是一个相位误差控制系统,利用反馈控制原理实现频率及相位的同步技术

锁相环通过比较输入信号和压控振荡器输出频率之间的相位差,产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频

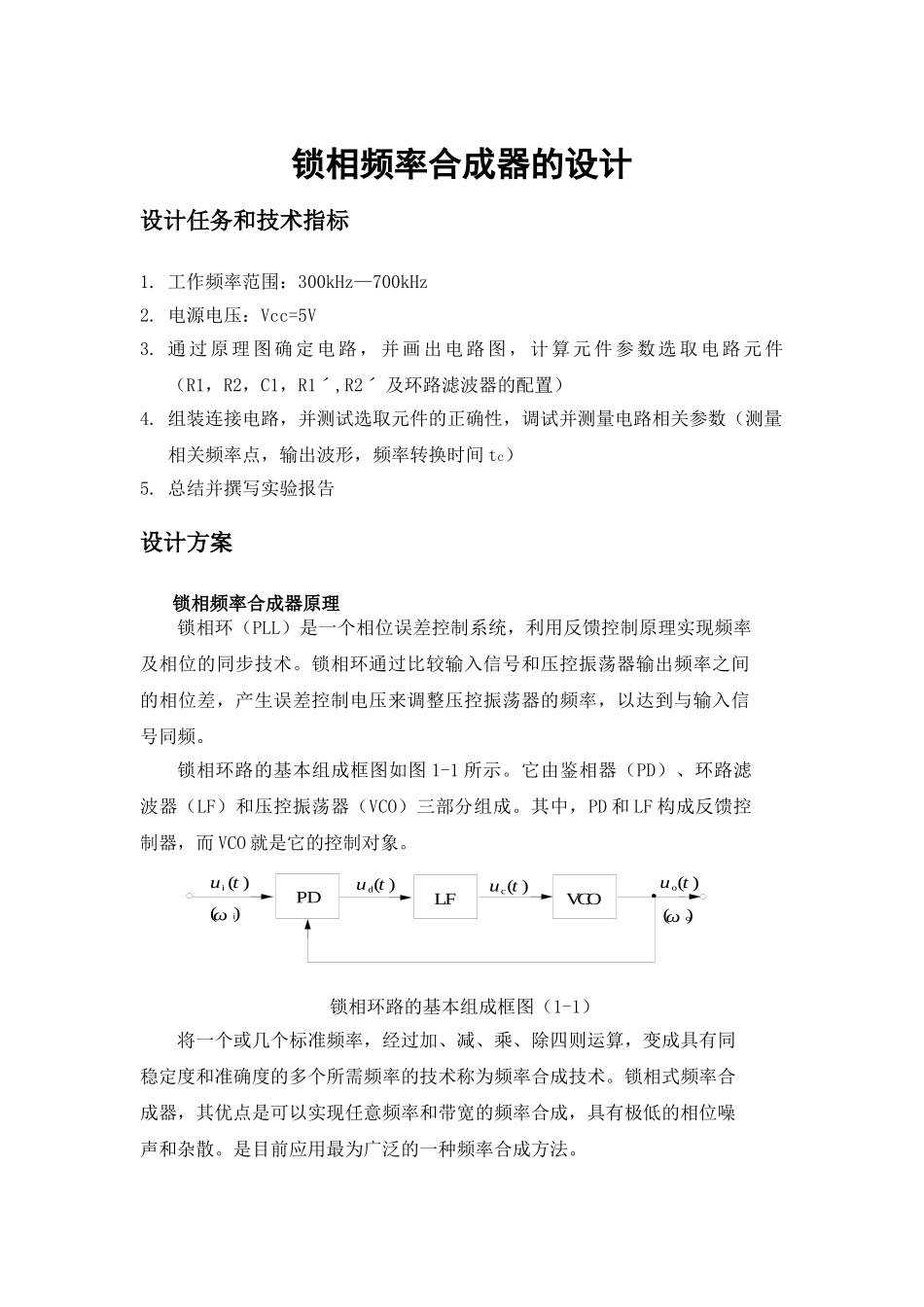

锁相环路的基本组成框图如图 1-1 所示

它由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成

其中,PD 和 LF 构成反馈控制器,而 VCO 就是它的控制对象

( ) u tiPD LF VCO( )u td( )u tc( )u to( )ω i( )ω o锁相环路的基本组成框图(1-1)将一个或几个标准频率,经过加、减、乘、除四则运算,变成具有同稳定度和准确度的多个所需频率的技术称为频率合成技术

锁相式频率合成器,其优点是可以实现任意频率和带宽的频率合成,具有极低的相位噪声和杂散

是目前应用最为广泛的一种频率合成方法

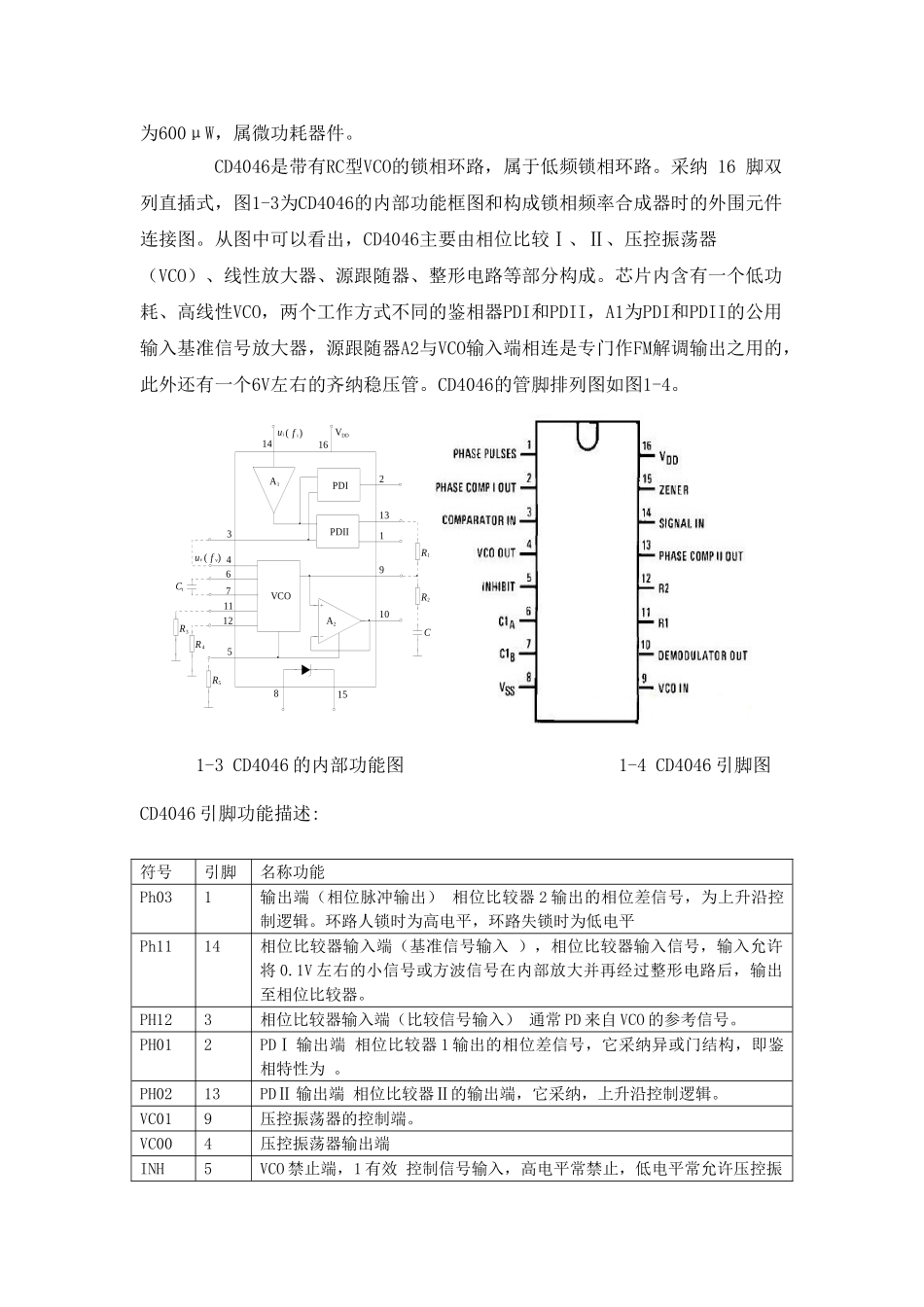

典型的直接式频率合成器组成框图如图 1-2 所示

它由参考振荡器、参考分频器、鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可编程分频器等部分组成

直接式频率合成器(图 1-2)由图1-2可知,晶体振荡器的频率经过M固定分频后得到步进参考频率,将信号作为鉴相器的基准与N分频器的输入进行比较,鉴相器的输出Ud正比于两路输入信号的相位差,Ud经过环路滤波器得到一个平均电压Uc,Uc控制压控振荡器(VCO)频率的变化,使鉴相器的两路输入信号相