数字频率计设计报告书一、设计要求设计一个4位十进制数字式频率计,最大测量范围为10MHz

量程分10kHz、100kHz、1MHz和10MHz四档(最大读数分别为9.999kHz、99.99kHz、999

9kHz、9999

量程自动转换规则如下:(1)当读数大于9999时,频率计处于超量程状态,此时显示器发出溢出指示,下一次测量时,量程自动增大一档,小数点位置随量程变更自动移位

(2)可用手动方式使量程在每次测量开始时处于最低档

显示方式如下:(3)采用记忆显示方式,即计数过程中不显示数据,待计数过程结束以后,显示计数结果,将此显示结果保持到下一次计数结束

显示时间应不小于1s

(4)送入信号应是符合CMOS电路要求的脉冲波,对于小信号模拟信号应有放大整形电路

二、方案设计整体思路所谓频率就是周期性信号在单位时间(1s)内变化的次数

若在一定时间间隔T内测得周期性信号的重复变化次数为N,则频率可表示为f=N/T(Hz)

被测信号fx经放大整形电路变成计数电路所要求的脉冲信号,其频率与被测信号fx的频率相同

基准电路提供标准时间基准信号clk,其高电平持续时间t1=1s,当1s信号来到时,闸门电路开通,被测脉冲信号通过闸门电路,成为计数电路的计数脉冲CP,计数电路开始计数,直到ls信号结束时闸门电路关闭,停止计数

若在闸门时间1s内计数电路计得的脉冲个数为N,则被测信号频率f=NHz

控制电路的作用有两个:一是产生锁存脉冲CLK,使显示电路上的数字稳定;二是产生清“0”脉冲,使计数电路每次测量从零开始计数

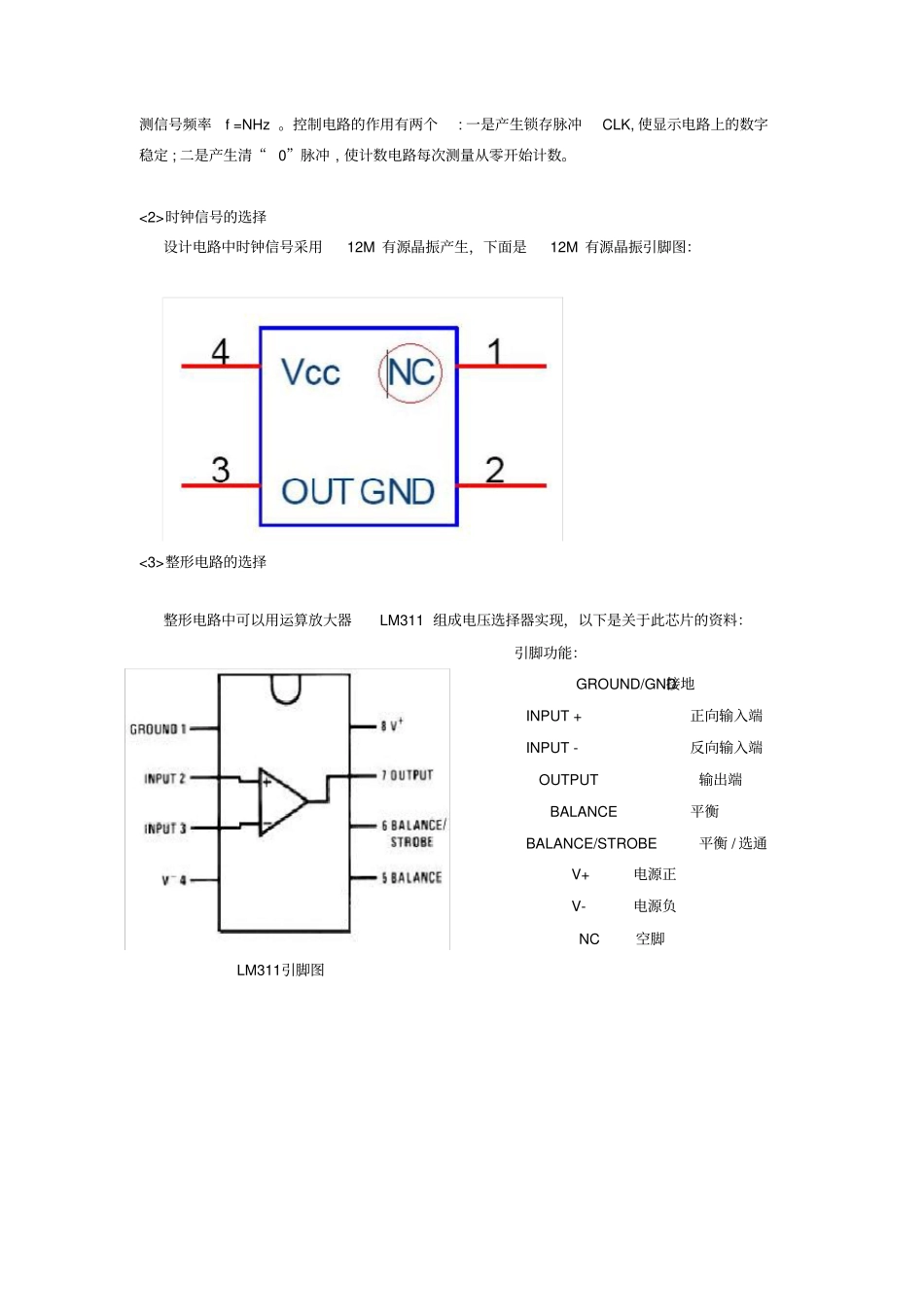

时钟信号的选择设计电路中时钟信号采用12M有源晶振产生,下面是12M有源晶振引脚图:整形电路的选择整形电路中可以用运算放大器LM311组成电压选择器实现,以下是关于此芯片的资料:引脚功能:GROUND/GND接地INPUT+正向输入端INPUT-反向输入端OUT