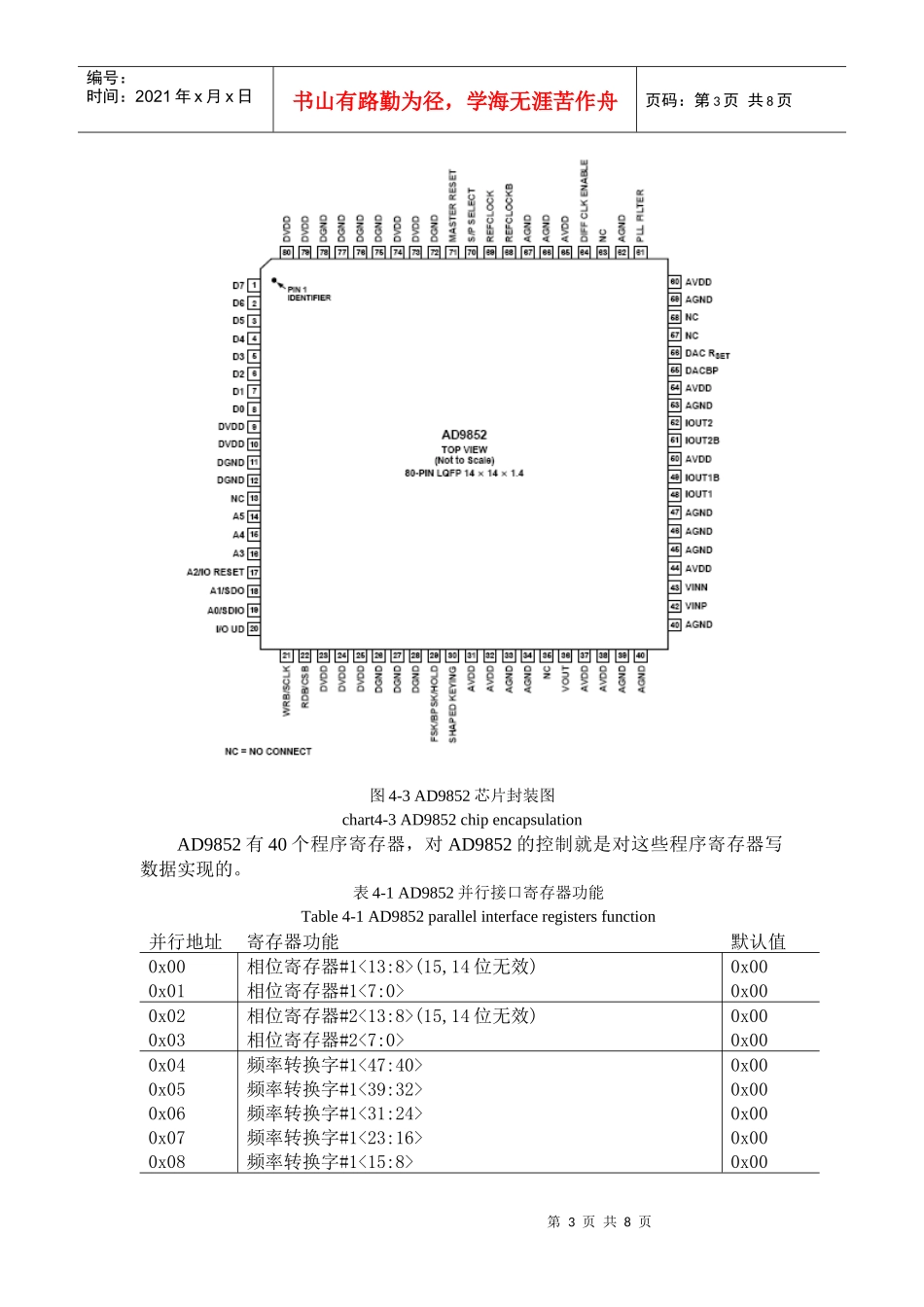

第1页共8页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共8页AD9852的引脚说明:D7—D0:Pin1—8,并行编程模式下的8位并行数据I/O口

A0—A5:Pin14—19,并行编程模式下的6位并行地址口

其中,Pin17与串行通信的复位端复用,Pin18与串行数据输出口复用(3线模式),Pin19与串行数据I/O口复用((2线模式)

DVDD:Pin9,10,23,24,25,73,74,79,80,数字电路电源端,相对于数字地3

3V供电,3

135V—3

465V可保证设计指标

DGND:Pinll,12,26,27,28,72,75,76,77,78,数字地

AVDD:Pin31,32,37,38,44,50,54,60,65,模拟电路电源端,相对于模拟地3

3V供电,3

135V—3

465V可保证设计指标

电路设计时,应加强DVDD和AVDD之间的去藕,以防噪声相互串扰

AGND:Pin33,34,39,40,41,45,46,47,53,59,62,66,67,模拟地

NC:Pin13,35,57,58,63,内部无连接的引脚,布线时可以悬空

I/OUD:Pin20,频率更新端口

要向AD9852寄存器内写数据,先是写到端口的缓冲器里,等工作模式所需的数据写完后,再在此引脚上加一持续至少8个系统时钟周期的高电平,使DDS芯片按照所设置的方式运行

频率更新也可以设置成内部更新模式,这时DDS按照UDC寄存器设置的值定时自动更新频率,同时输出持续8个系统时钟周期高电平的同步信号

WRB/SCLK:Pin21,并行模式下的读控制端,与串行模式时钟信号输入端复用

RDB/CSB:Pin22,并行模式下的写控制端,与串行模式片选端复用

FSK/BPSK/HOLD:Pin29,多功能复用引脚

FSK工作模式下,低电平选择频率F1,高电平选