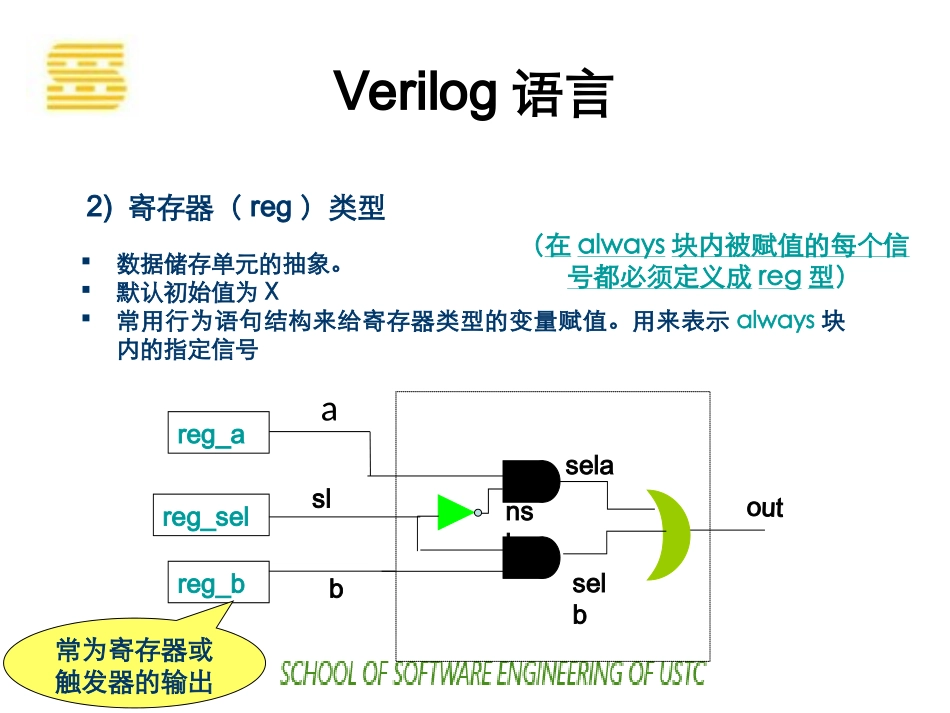

sl1)Net(网络连线):由模块或门驱动的连线。驱动端信号的改变会立刻传递到输出的连线上。例如:右图上,selb的改变,会自动地立刻影响或门的输出。netsabselbselanslout如果不明确地说明连接是何种类型,应该是指wire类型。Verilog语言2)寄存器(reg)类型数据储存单元的抽象。默认初始值为X常用行为语句结构来给寄存器类型的变量赋值。用来表示always块内的指定信号abslselbnsloutreg_areg_selreg_b常为寄存器或触发器的输出Verilog语言(在always块内被赋值的每个信号都必须定义成reg型)sela格式:reg[n-1:0]数据名1,数据名2,……,数据名i;或reg[n:1]数据名1,数据名2,……,数据名i;例:regrega;reg[3:0]regb,regc;可以赋正值也可以赋负值,但当一个reg型数据是一个表达式中的操作数时,它的值被当作无符号值,即正值。如regb被赋值为-1,在表达式中被认为是??Verilog语言例:寄存器的声明和使用regreset;initialbeginreset=1`b1;#100reset=1`b0;endregsigned[63:0]m;integeri;Verilog语言3)整数、实数和时间寄存器类型integer(通用寄存器数据类型,用于对数量进行操作)例:integercounter;//一般用途,做为计数器initalcounter=-1;real实常量和实寄存器数据类型使用,默认值为0例:realdelta;realdelta;initialinitialbeginbegindelta=4e10;delta=4e10;delta=2delta=2..13;13;endendintegeri;integeri;initialinitiali=delta;//ii=delta;//i的的值为值为22Verilog语言time保存仿真时间,通过系统函数$time可以得到当前的仿真时间例:timesve_sim_time;initialsave_sim_time=$time;4)向量线网和寄存器类型的数据均可声明为向量(位宽大于1)。若没有指定位宽,则默认为标量(1位)。例:wirea;wire[7:0]bus;wire[31:0]busA,busB,busC;regclock;reg[0:40]virtual_addr;//最高有效位为第0位Verilog语言向量域选择对上例中向量,可以指定它的某一位或若干个相邻位busA[7]bus[2:0]//不可以写成bus[0:2],高位应写在范围说明的左侧virtual_addr[0:1]可变的向量域选择[+:width]从起始位开始递增,位宽为width[-:width]从起始位开始递减,位宽为widthVerilog语言Verilog语言reg[255:0]data1;reg[0:255]data2;reg[7:0]byte;byte=data1[31-:8];从第31位算起,宽度为8位,相当于data1[31:24]byte=data1[24+:8];byte=data2[31-:8];从第31位算起,宽度为8位,相当于data1[24:31]byte=data2[24+:8];//起始位可以是变量,但宽度必须为常数for(j=0;j<=31;j=j+1)byte=data1[(j*8)+:8];data1[(byteNum*8)+:8]=8`b0;5)数组Verilog中允许声明reg,integer,time,real,realtime及其向量类型的数组,对数组的维数没有限制,线网数组也可用于连接实例的端口integercount[0:7];regbool[31:0];timechk_point[1:100];//由100个时间检查变量组成的数组reg[4:0]port_id[0:7];//由8个端口标识变量组成的数组,端口变量的位宽为5integermatrix[4:0][0:255];//二维的整数型数组reg[63:0]array_4d[15:0][7:0][7:0][255:0];//四维64位寄存器型数组wire[7:0]w_array1[7:0][5:0];//声明8位线型变量的二维数组Verilog语言count[5]=0;chk_point[100]=0;port_id[3]=0;matrix[1][0]=33559;//第1行第0列的整数型单元置为33559array_4d[0][0][0][0][15:0]=0;//把四维数组中索引号为[0][0][0][0]的寄存器型单元的0~15位置为0port_id=0;//非法matrix[1]=0;//非法Verilog语言6)memory类型通过扩展reg型数据的地址范围生成格式:reg[n-1:0]存储器名[m-1:0];或者reg[n-1:0]存储器名[m:1];例:reg[7:0]memea[255:0];必须为常数表达式Parameterwordsize=16,memsize=256;reg[wordsize-1:0]mem[memsize-1:0],wreitereg,readreg;Verilog语言注意:reg[n-1:0]rega;regmema[n-1:0];rega=0;等于等于mema=0;????mema[3]=0;正确??正确??Verilog语言7)参数使用关键字parameter在模块内定义常数,不能像变量那样赋值,但每个模块实例的参数值可以在编译阶段被重载(defparam)parametercache_line_width=256;//定义高速缓冲器宽度parametersigned[15:0]WIDTH;//把参数WIDTH规...