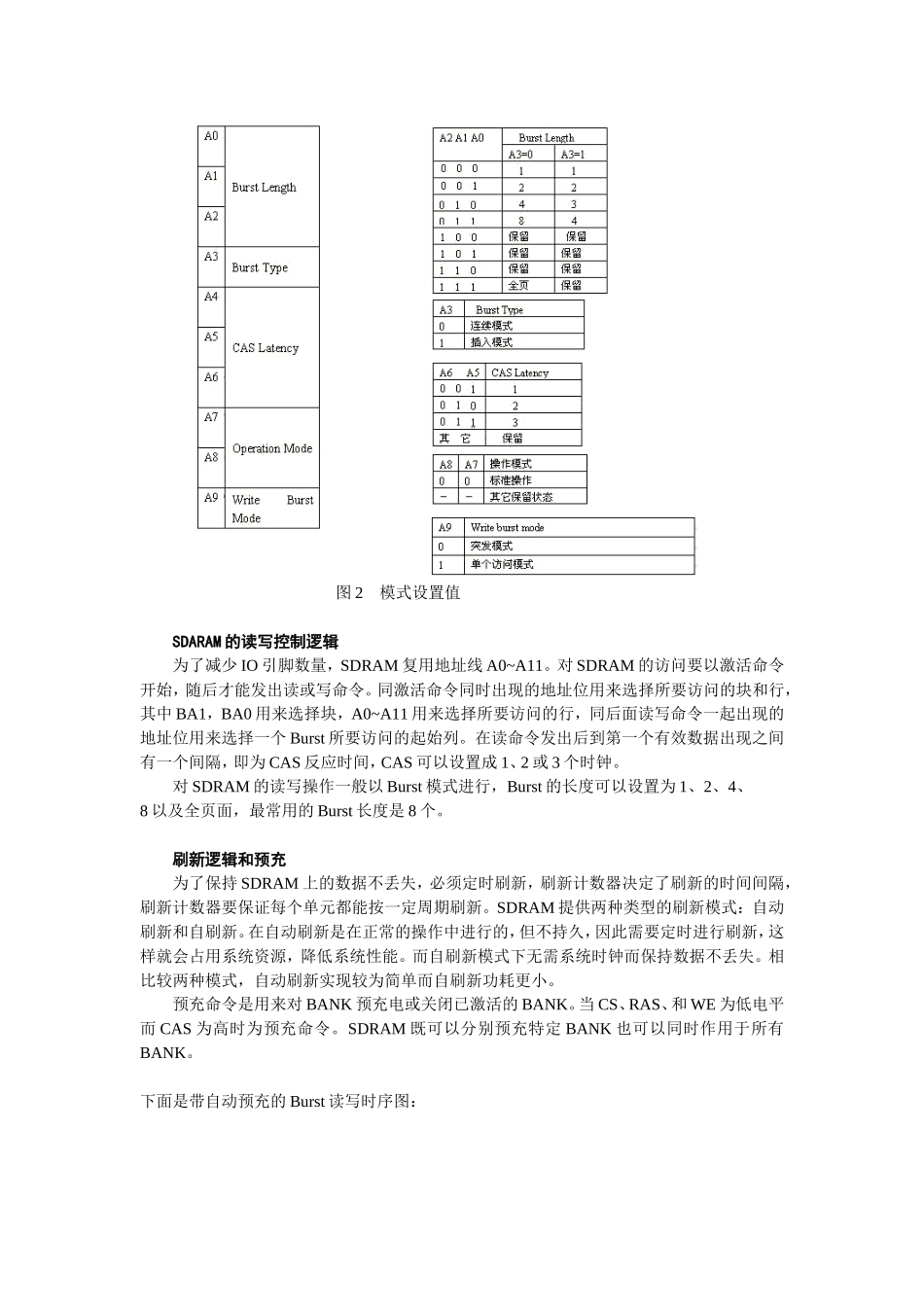

SDRAM的控制时序SDRAM需要正确的上电逻辑和模式设置来进入期望的工作模式。访问特定的逻辑单元必须先激活相应的存储块,并锁定对应的行列地址。另外,必须有定时的刷新逻辑保持数据不丢失,SDRAM有多种操作模式,由引脚CS#、RAS#、CAS#、WE#和地址信号的不同状态来决定,SDRAM控制器必须为SDRAM提供满足时序要求的这些控制信号,以准确地控制SDRAM的各种不同操作。图1SDRAM操作命令表SDRAM初始化和模式设置SDRAM的所有电源引脚必须同时加电,并且所有输入和电源引脚上电电压不得超过标称值0.3V。加电完成后应等待100us之后再对所有BANK进行预充电,等待期间要求CKE保持高电平。预充电之后要执行两个自动刷新命令,之后发出模式设置命令以初始化模式寄存器。由于在上电后模式寄存器的状态是不确定的,所以在进行SDRAM操作之前一定要先设置模式寄存器。模式设置命令使用地址线A10~A0作为模式数据输入线。其中A2~A0作为Burst长度,A3为Burst类型,A6~A4为CAS延迟。A8~A7为操作模式,A9为写Burst模式。模式寄存器的设置值必须与器件的延迟参数以及读写操作的控制时序一致。模式寄存器的设置值如下表所示。图2模式设置值SDARAM的读写控制逻辑为了减少IO引脚数量,SDRAM复用地址线A0~A11。对SDRAM的访问要以激活命令开始,随后才能发出读或写命令。同激活命令同时出现的地址位用来选择所要访问的块和行,其中BA1,BA0用来选择块,A0~A11用来选择所要访问的行,同后面读写命令一起出现的地址位用来选择一个Burst所要访问的起始列。在读命令发出后到第一个有效数据出现之间有一个间隔,即为CAS反应时间,CAS可以设置成1、2或3个时钟。对SDRAM的读写操作一般以Burst模式进行,Burst的长度可以设置为1、2、4、8以及全页面,最常用的Burst长度是8个。刷新逻辑和预充为了保持SDRAM上的数据不丢失,必须定时刷新,刷新计数器决定了刷新的时间间隔,刷新计数器要保证每个单元都能按一定周期刷新。SDRAM提供两种类型的刷新模式:自动刷新和自刷新。在自动刷新是在正常的操作中进行的,但不持久,因此需要定时进行刷新,这样就会占用系统资源,降低系统性能。而自刷新模式下无需系统时钟而保持数据不丢失。相比较两种模式,自动刷新实现较为简单而自刷新功耗更小。预充命令是用来对BANK预充电或关闭已激活的BANK。当CS、RAS、和WE为低电平而CAS为高时为预充命令。SDRAM既可以分别预充特定BANK也可以同时作用于所有BANK。下面是带自动预充的Burst读写时序图:图3带自动预充的Burst读时序基于FPGA的SDRAM控制器设计SDRAM的控制时序是很复杂的,上面所列出的远非全部。但针对特定的系统不可能把所有的功能都用到,只是用到部份必要的功能。笔者针对系统设计的需要定制了必需的SDRAM的功能,如下所示:1.支持Burst长度为8的读写操作。2.自动刷新3.初始化4.读、写、自动刷新和初始化之间的优先级仲裁机制以及转换机制。具有以上功能的SDRAM控制器可以满足系统对SDRAM访问的需要,同时舍去了对系统无用的功能。这样不仅可以减小开发难度,还可以节省系统资源和成本,提升系统的性能。下面分别阐述每项功能的设计要点:初始化上电之后外部产生Reset命令送给SDRAM控制器,SDRAM控制器由此进入初始化状态。对SDRAM进行初始化执行一系列操作,完成上电、预充电、自动刷新和模式寄存器设置,在进行Verilog程序设计时,可以通过状态机来实现这一过程。图4初始化状态机其中NOP指的是空操作,具体等待长度可以查看相关芯片资料,在此不作详述。自动刷新SDRAM要求定时进行刷新,以保持数据不丢失,以MICRON的MT48LC4M32B2YG-7芯片为例,共需4K刷新周期/64ms,即每15.625us刷新一次才能满足需要。SDRAM采用的是33M的PCI总线时钟,即每420个时钟周期启动一次刷新命令,为此本文在SDRAM控制器中设置一个定时器,每计数到420便发出刷新命令。同样刷新操作也是由一系列SDRAM命令来组成的,每次启动刷新操作时要先进行预充电,随后再执行两个自动刷新命令即完成一次刷新操作。在Verilog中可用如下状态机来实现自动刷新:图5刷新状态机读写控制逻辑SDRAM采用地址线行列复用技术,对于存储器单元的访问基于页面,而外...