随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计

在多层板的设计中,对于叠层的安排显得尤为重要

一个好的叠层设计方案将会大大减小EMI及串扰的影响,在下面的讨论中,我们将具体分析叠层设计如何影响高速电路的电气性能

一.多层板和铺铜层(Plane)多层板在设计中和普通的PCB板相比,除了添加了必要的信号走线层之外,最重要的是安排了独立的电源和地层(铺铜层)

在高速数字电路系统中,使用电源和地层来代替以前的电源和地总线的优点主要在于:1

为数字信号的变换提供一个稳定的参考电压

均匀地将电源同时加在每个逻辑器件上3

有效地抑制信号之间的串扰原因在于,使用大面积铺铜作为电源和地层大大减小了电源和地的电阻,使得电源层上的电压很均匀平稳,而且可以保证每根信号线都有很近的地平面相对应,这同时减小了信号线的特征阻抗,对有效地较少串扰也非常有利

所以,对于某些高端的高速电路设计,已经明确规定一定要使用6层(或以上的)的叠层方案,如Intel对PC133内存模块PCB板的要求

这主要就是考虑到多层板在电气特性,以及对电磁辐射的抑制,甚至在抵抗物理机械损伤的能力上都明显优于低层数的PCB板

如果从成本的因素考虑,也并不是层数越多价格越贵,因为PCB板的成本除了和层数有关外,还和单位面积走线的密度有关,在降低了层数后,走线的空间必然减小,从而增大了走线的密度,甚至不得不通过减小线宽,缩短间距来达到设计要求,往往这些造成的成本增加反而有可能会超过减少叠层而降低的成本,再加上电气性能的变差,这种做法经常会适得其反

所以对于设计者来说,一定要做到全方面的考虑

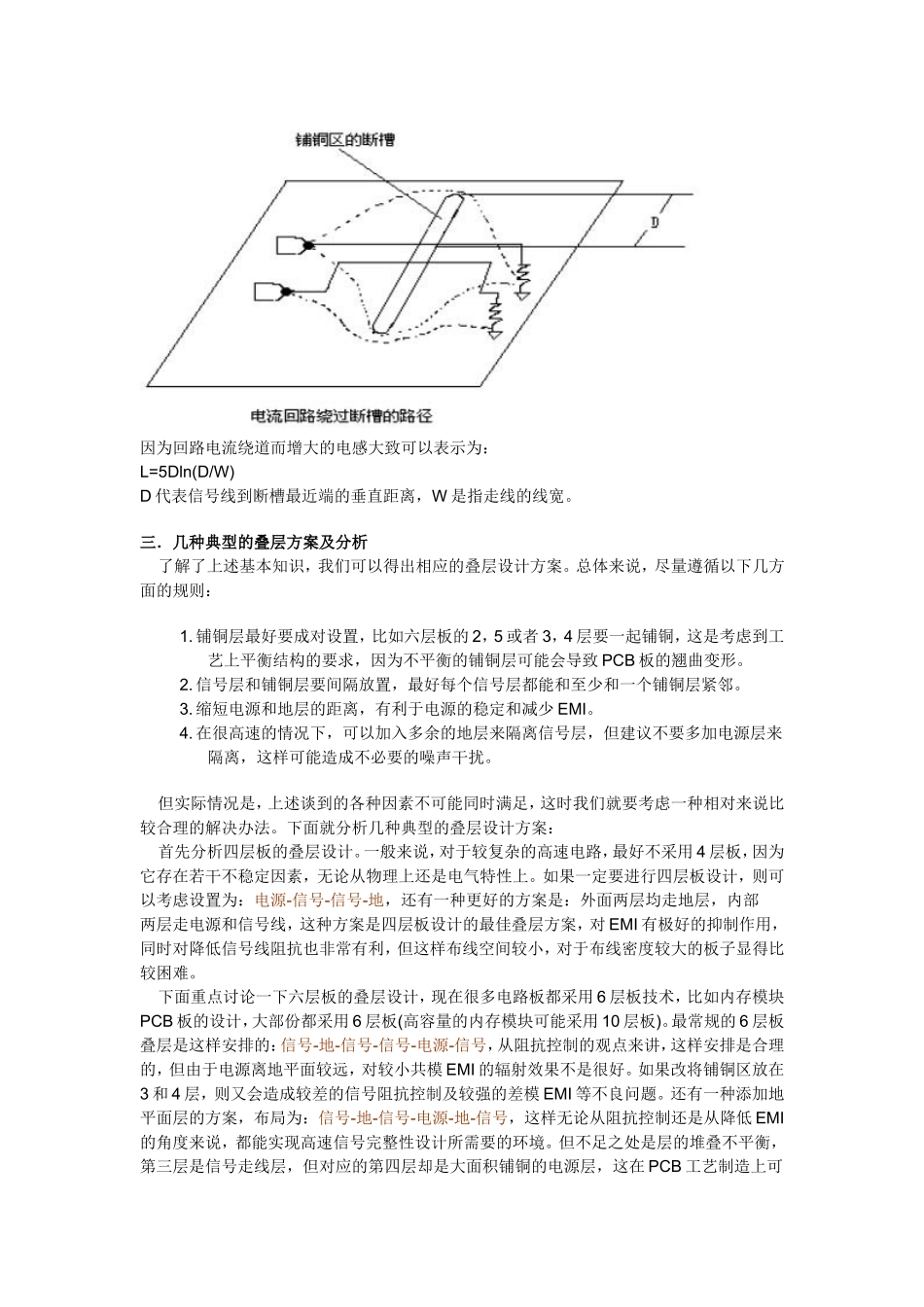

二.高频下地平面层对信号的影响如果我们将PCB的微带布线作为一个传输线模型来看,那么地平面层也可以看成是传输线的一部分,这里可以用“回路”的概念来代替“地”的概念,