实验一半加器设计一、实验目的1、理解和学习QuartusII5

1软件设计平台

2、理解EDA的设计过程

3、通过实例,学习和掌握QuartusII5

1平台下的图形输入法4、学习和掌握半加器的工作和设计原理

二、实验仪器PC机,操作系统为Windows/XP,本课程所用系统均为WindowsXP(下同),QuartusII5

三、实验原理加法器是构成算术运算器的基本单元,有来自低位的进位将两个1位二进制数相加,称为半加

实现半加运算的电路叫做半加器

按照二进制加法运算规则能够列出如表1-1所示的半加器真值表

其中A、B是两个加数,S是相加的和,CO是相加高位的进位

将S、CO、和A、B的关系写成逻辑体现式以下:因此,半加器是一种异或门和一种与门构成的简朴电路输入输出ABSCO0001101100101001表1-1半加器的真值表四、实验环节1、启动QuartusII5

1:在Windows操作系统下,单击“开始”,选择“程序”,再选择“altera”选项下的“QuartusII5

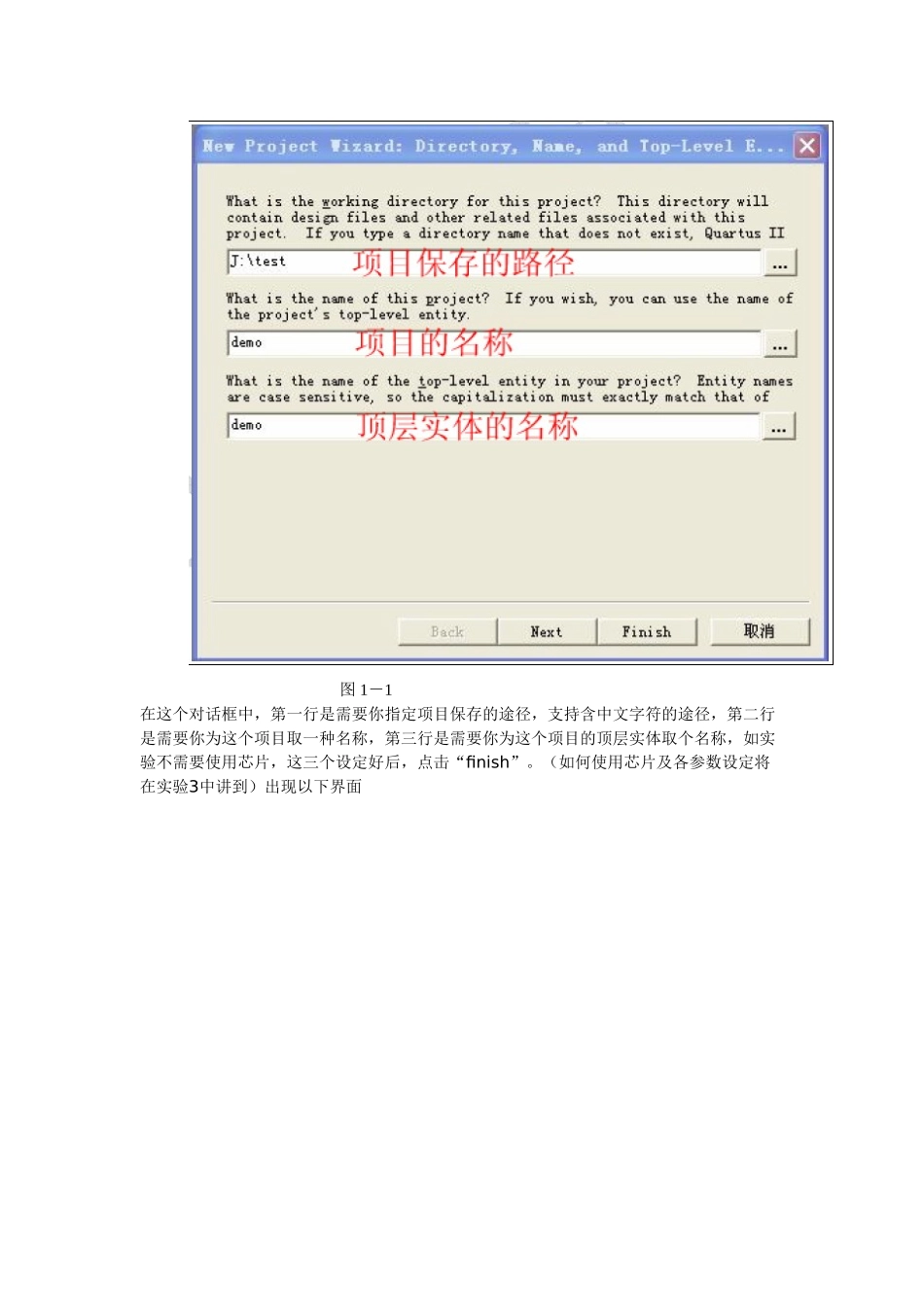

2、新建工程:在File菜单中选择NewProjectWizard…,弹出对话框如图1-1所示图1-1在这个对话框中,第一行是需要你指定项目保存的途径,支持含中文字符的途径,第二行是需要你为这个项目取一种名称,第三行是需要你为这个项目的顶层实体取个名称,如实验不需要使用芯片,这三个设定好后,点击“finish”

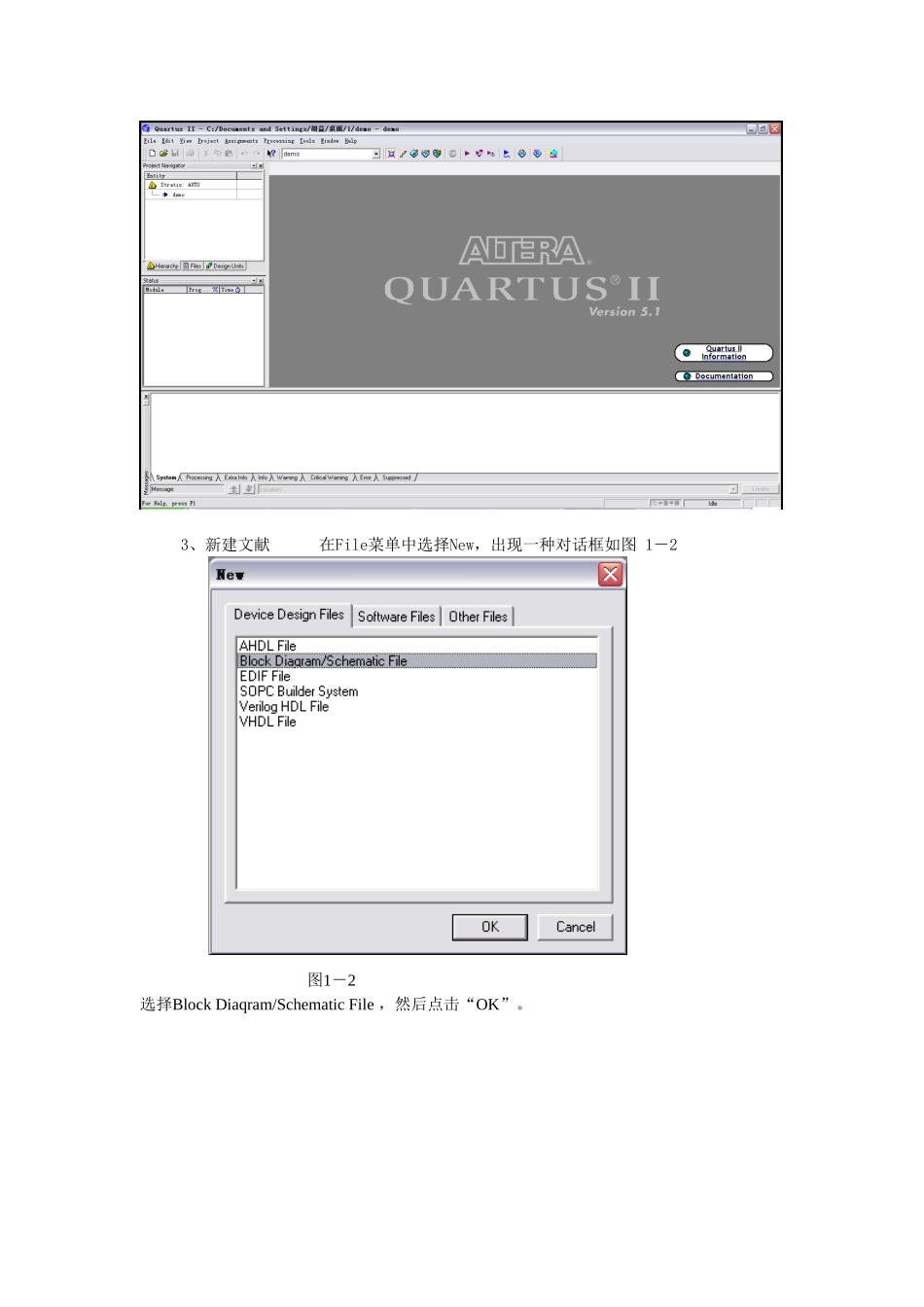

(如何使用芯片及各参数设定将在实验3中讲到)出现以下界面3、新建文献在File菜单中选择New,出现一种对话框如图1-2图1-2选择BlockDiaqram/SchematicFile,然后点击“OK”

图1-34、保存文献:选菜单File\Save,在弹出的SaveAs对话窗口中,指定寄存文献类型、文献夹和文献名

这一步也能够放在图形设计完毕后进行

5、原理图设计