题目:设计数字电子钟专业:电子信息工程姓名:石常兴指导老师:时间:2006数字钟的设计设计任务与要求一、基本要求1、设计一台能准确计时,以数字形式显示时、分、秒的时间,要求24小时为一计时周期

2、当电路发生走时误差时,要求电路具有校时功能

3、要求电路具有整点报时功能,报时声响为四低一高,最后一响正好为整点

二、设计内容1.电路各部分的组成及工作原理

2.元器件的选取及其电路图和功能

3.电路各部分的调试方法

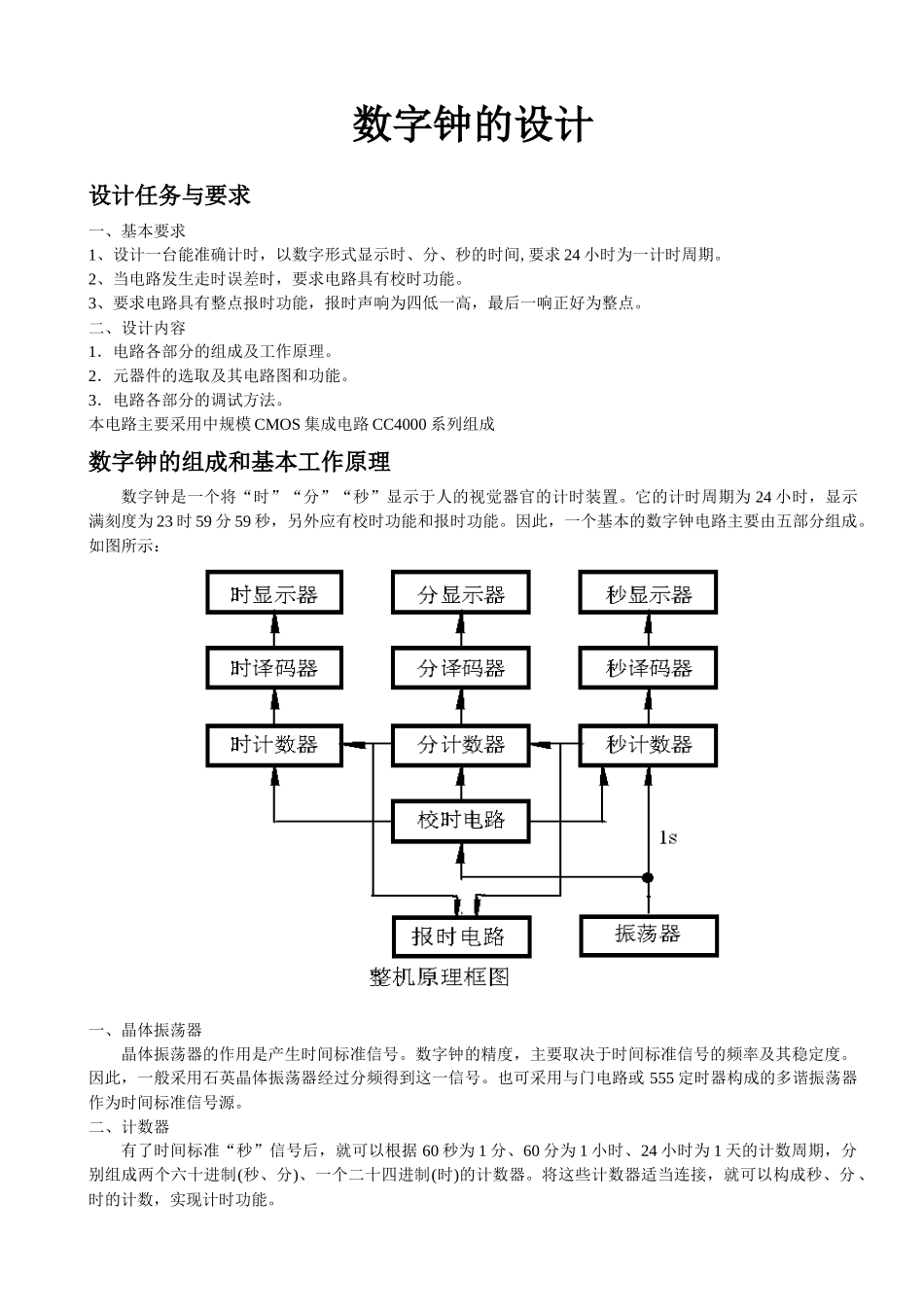

本电路主要采用中规模CMOS集成电路CC4000系列组成数字钟的组成和基本工作原理数字钟是一个将“时”“分”“秒”显示于人的视觉器官的计时装置

它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能

因此,一个基本的数字钟电路主要由五部分组成

如图所示:一、晶体振荡器晶体振荡器的作用是产生时间标准信号

数字钟的精度,主要取决于时间标准信号的频率及其稳定度

因此,一般采用石英晶体振荡器经过分频得到这一信号

也可采用与门电路或555定时器构成的多谐振荡器作为时间标准信号源

二、计数器有了时间标准“秒”信号后,就可以根据60秒为1分、60分为1小时、24小时为1天的计数周期,分别组成两个六十进制(秒、分)、一个二十四进制(时)的计数器

将这些计数器适当连接,就可以构成秒、分、时的计数,实现计时功能

三、译码和数码显示电路译码和数码显示电路是将数字钟的计时状态直观清晰地反映出来,被人们的视觉器官所接受

显示器件选用LED七段数码管

在译码显示电路输出信号的驱动下,显示出清晰、直观的数字符号

四、校时电路实际的数字钟电路由于秒信号的精确性和稳定性不可能做到完全(绝对)准确无误,加之电路中其它原因,数字钟总会产生走时误差的现象

因此,电路中就应该有校准时间功能的电路

五、报时电路当数字钟显示整点时,应能报时

要求当数字钟的“分”和“秒”计数器计到59