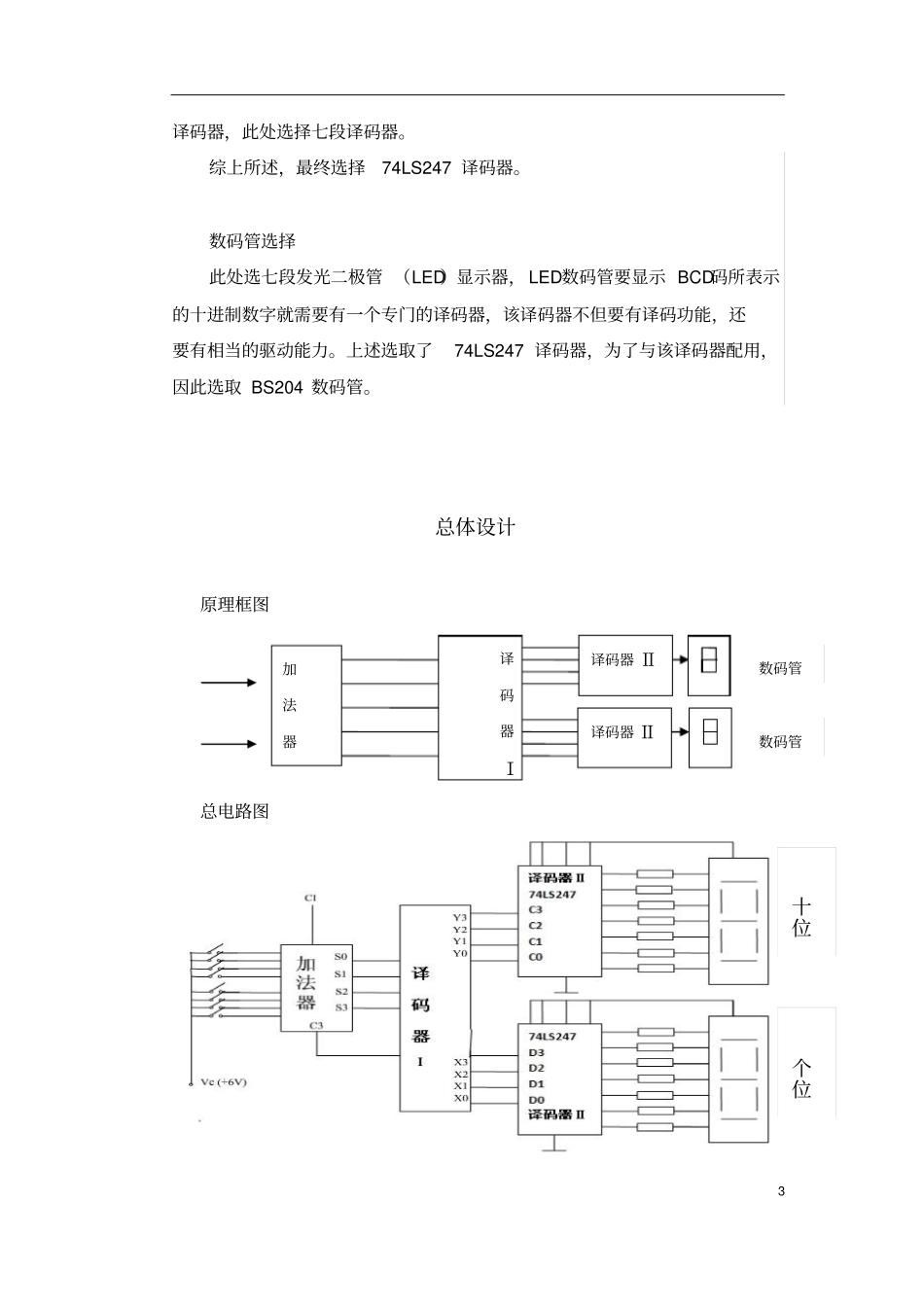

1 课题名称与技术要求课题名称 :四位二进制加法器设计技术要求 :1)四位二进制加数与被加数输入2)二位数码管显示摘要本设计通过八个开关将A3,A2,A1,A0和 B3,B2,B1,B0信号作为加数和被加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位C3通过译码器Ⅰ译码, 再将输出的 Y3,Y2,Y1,Y0 和 X3,X2,X1,X0 各自分别通过一个 74LS247译码器,最后分别通过数码管BS204实现二位显示

本设计中译码器Ⅰ由两部分组成,包括五位二进制译码器和八位二进制输出器

信号 S3,S2,S1,S0和向高位的进位C3输入五位二进制 - 脉冲产生器,将得到的 n(五位二进制数码对应的十进制数)个脉冲信号输入八位二进制输出器,使电路的后续部分得以执行

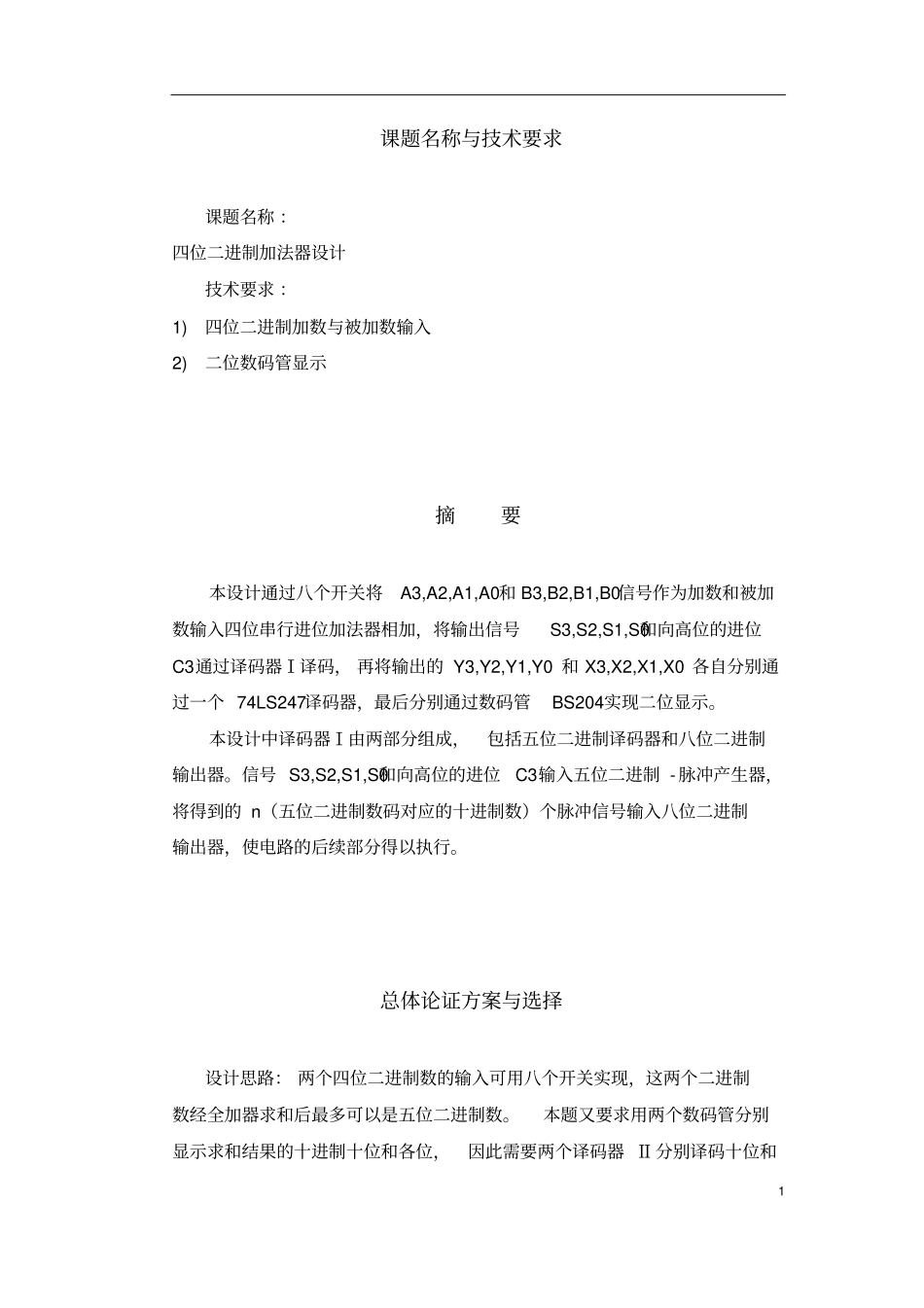

总体论证方案与选择设计思路: 两个四位二进制数的输入可用八个开关实现,这两个二进制数经全加器求和后最多可以是五位二进制数

本题又要求用两个数码管分别显示求和结果的十进制十位和各位,因此需要两个译码器 Ⅱ分别译码十位和2 个位

综上所述,需要设计一个译码器Ⅰ,能将求和得到的五位二进制数译成八位,其中四位表示这个五位二进制数对应十进制数的十位,另四位表示个位

而译码器 Ⅱ有现成的芯片可选用,此处可选74LS247,故设计重点就在译码器Ⅰ

加法器选择全加器 :能对两个 1 位二进制数进行相加并考虑低位来的进位,即相当于3个 1 位二进制数相加,求得和及进位的逻辑电路称为全加器

或:不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器

1)串行进位加法器构成:把 n 位全加器串联起来,低位全加器的进位输出连接到相邻的高位全加器的进位输入

优点:电路比较简单

最大缺点:进位信号是由低位向高位逐级传递的,运算速度慢

2)超前进位加法器为了提高运算速度,必须设法减小或消除由