P CI-E 布线规则 1、从金手指边缘到 PCIE 芯片管脚的走线长度应限制在 4 英寸(约 100MM)以内

2、PCIE 的 PERP/N,PETP/N,PECKP/N 是三个差分对线,注意保护(差分对之间的距离、差分对和所有非 PCIE 信号的距离是 20MIL,以减少有害串扰的影响和电磁干扰(EMI)的影响

芯片及 PCIE 信号线反面避免高频信号线,最好全 GND)

3、差分对中 2 条走线的长度差最多 5MIL

2 条走线的每一部分都要求长度匹配

差分线的线宽 7MIL,差分对中 2 条走线的间距是 7MIL

4、当 PCIE 信号对走线换层时,应在靠近信号对过孔处放置地信号过孔,每对信号建议置 1 到 3 个地信号过孔

PCIE 差分对采用 25/14 的过孔,并且两个过孔必须放置的相互对称

5、PCIE 需要在发射端和接收端之间交流耦合,差分对的两个交流耦合电容必须有相同的封装尺寸,位置要对称且要摆放在靠近金手指这边,电容值推荐为0

1uF,不允许使用直插封装

6、SCL 等信号线不能穿越 PCIE 主芯片

合理的走线设计可以信号的兼容性,减小信号的反射和电磁损耗

PCI-E 总线的信号线采用高速串行差分通信信号,因此,注重高速差分信号对的走线设计要求和规范,确保 PCI-E 总线能进行正常通信

PCI-E 是一种双单工连接的点对点串行差分低电压互联

每个通道有两对差分信号:传输对 Txp/Txn,接收对 Rxp/Rxn

该信号工作在 2

5 GHz 并带有嵌入式时钟

嵌入式时钟通过消除不同差分对的长度匹配简化了布线规则

随着 PCI-E 串行总线传输速率的不断增加,降低互连损耗和抖动预算的设计变得格外重要

在整个 PCI-E 背板的设计中,走线的难度主要存在于 PCI-E 的这些差分对

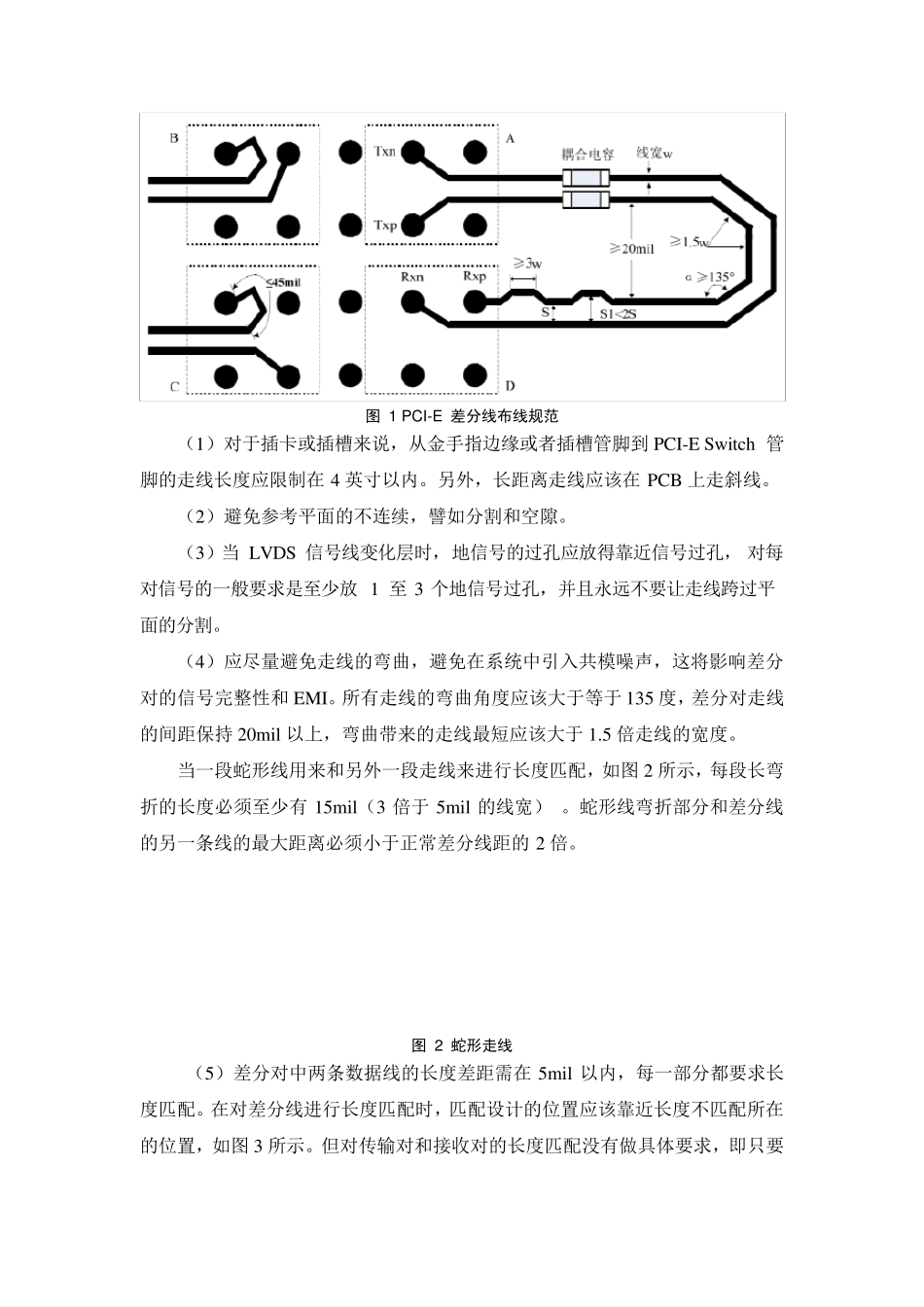

图 1 提供了 PCI-E 高速串行信号差分对走线中