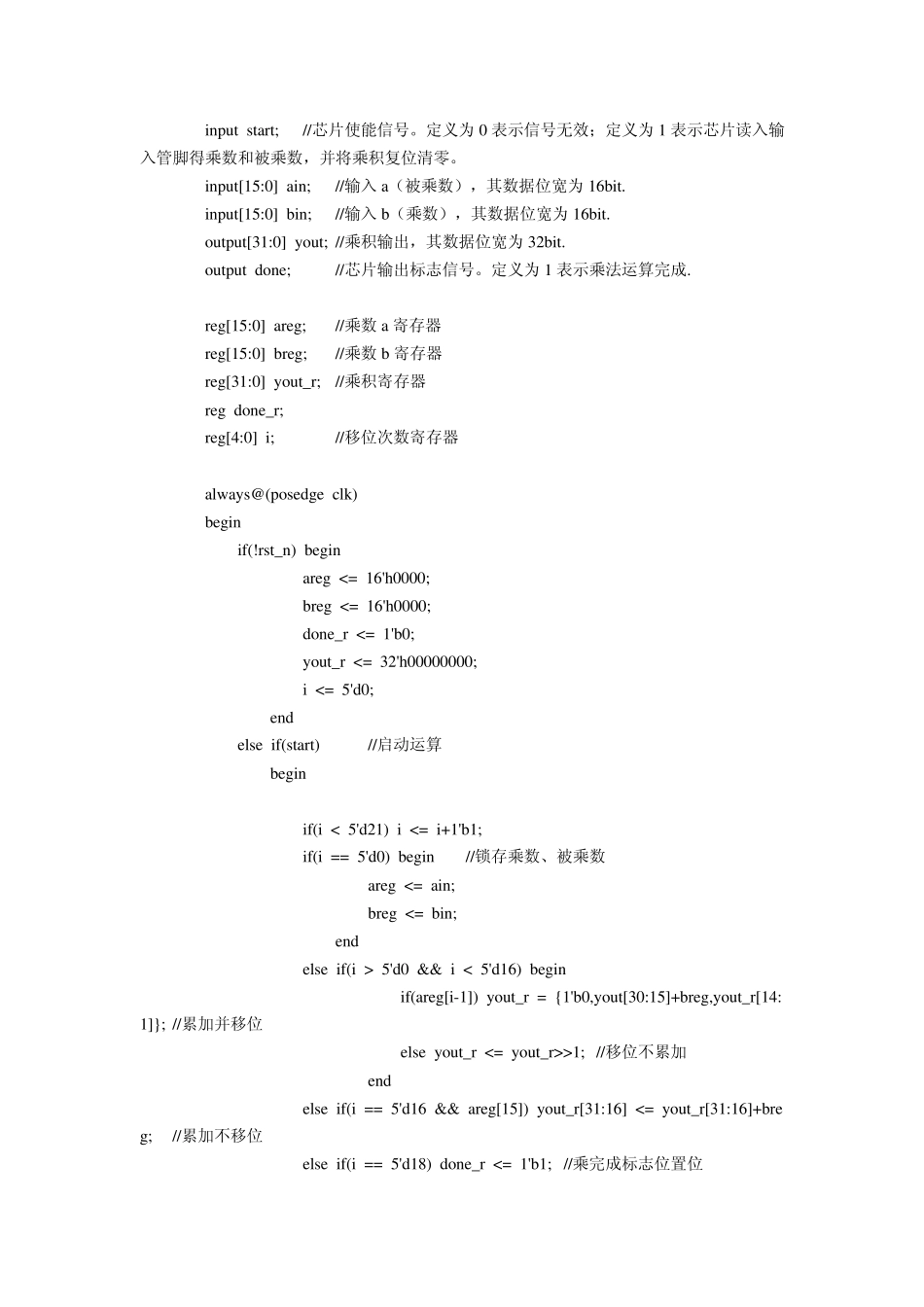

乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴;但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑范畴。 通过这个实验使大家能够掌握利用 FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。下面我们分别列举了十进制乘法运算和二进制乘法运算的例子。下面这种计算乘法的方式是大家非常熟悉的:乘积项与乘数相应位对齐(即将乘积项左移),加法运算的数据宽度与被乘数的数据位宽相同。 下面例子中的被乘数和乘数都是无符号的整数,对于有符号数的乘法,可以将符号与数据绝对值分开处理,即绝对值相乘,符号异或。乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。采用组合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。 在本次实验中我们就利用时序逻辑设计方法来设计一个 16位乘法器,既然是利用时序逻辑设计方法那么我们就得利用时钟信号控制乘法器运算,那么这样用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在实际工程设计中。 IO口定义: clk:芯片的时钟信号。 rst_n:低电平复位、清零信号。定义为 0表示芯片复位;定义为 1表示复位信号无效。 start: 芯片使能信号。定义为 0表示信号无效;定义为 1表示芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。 ain:输入 a(被乘数),其数据位宽为 16bit. bin:输入 b(乘数),其数据位宽为 16bit. yout:乘积输出,其数据位宽为 32bit. done:芯片输出标志信号。定义为1表示乘法运算完成,yout端口的数据稳定,得到最终的乘积;定义为0表示乘法运算未完成,yout端口的数据不稳定。 数据吞吐量的计算: 数据吞吐量使指芯片在一定时钟频率条件下所能处理的有效数据量。 假设本实验设计的芯片时钟频率可达300MHz,那么该芯片的数据吞吐量是多少呢? 由于芯片完成一次乘法运算需要1个以上的时钟周期,因此,即使芯片采用300MHz的时钟频率,它每秒钟所能处理的有效数据吞吐量也一定小于300M。对于16位乘法器而言,ain和bin均为0xFFFF时,芯片的运算量最大,计算所需的时间也最长,这种情况才能作为我们计算数据吞吐量的依据。 假设芯片在200MHz的...