SignalTap IIw ith Verilog Designs1Introdu ctionThis tutorial explains how to use the SignalTap II feature within Altera’s Quartus ® II software

The SignalTap IIEmbedded Logic Analyzeris a system-level debugging tool that captures and displays signals in circuits designedfor implementation in Altera’s FPGAs

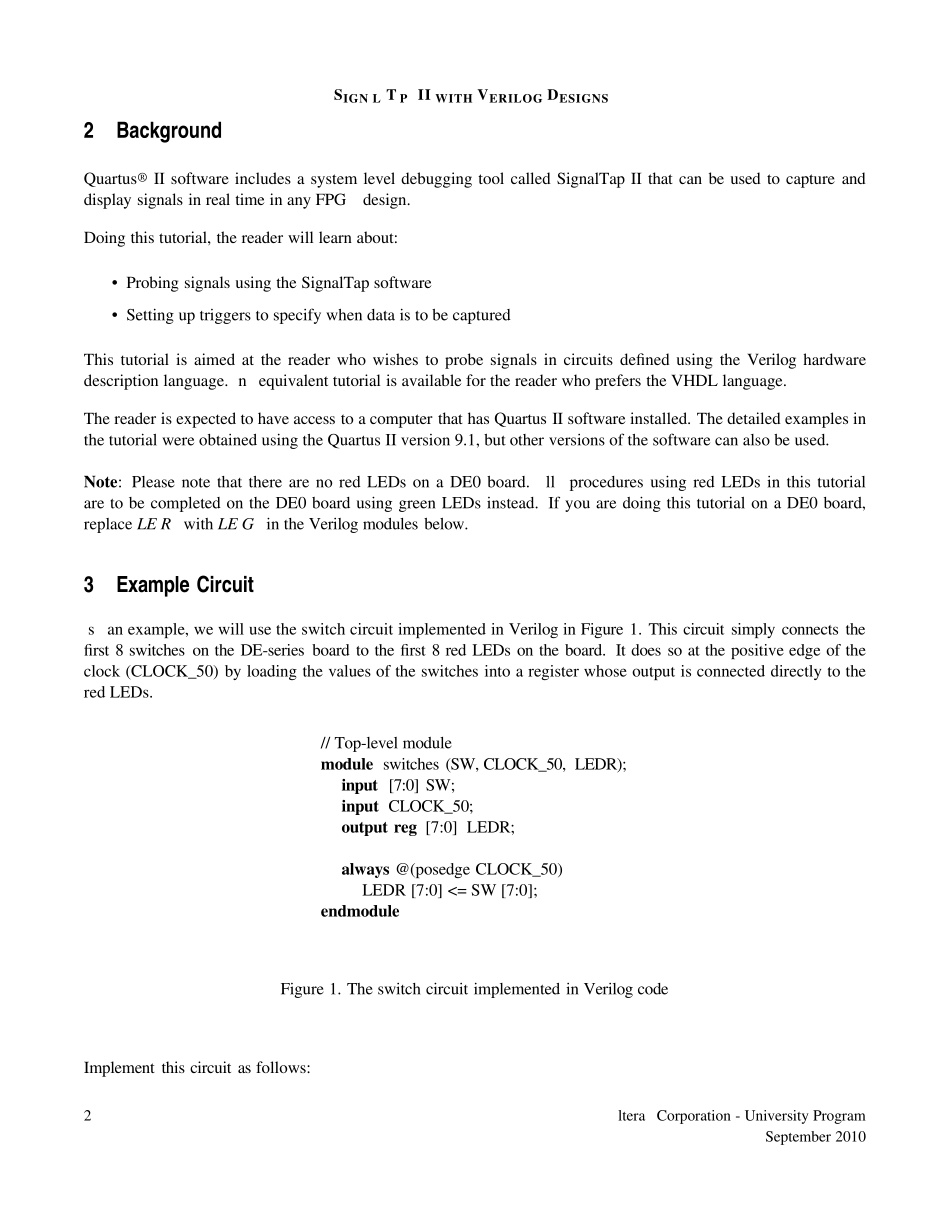

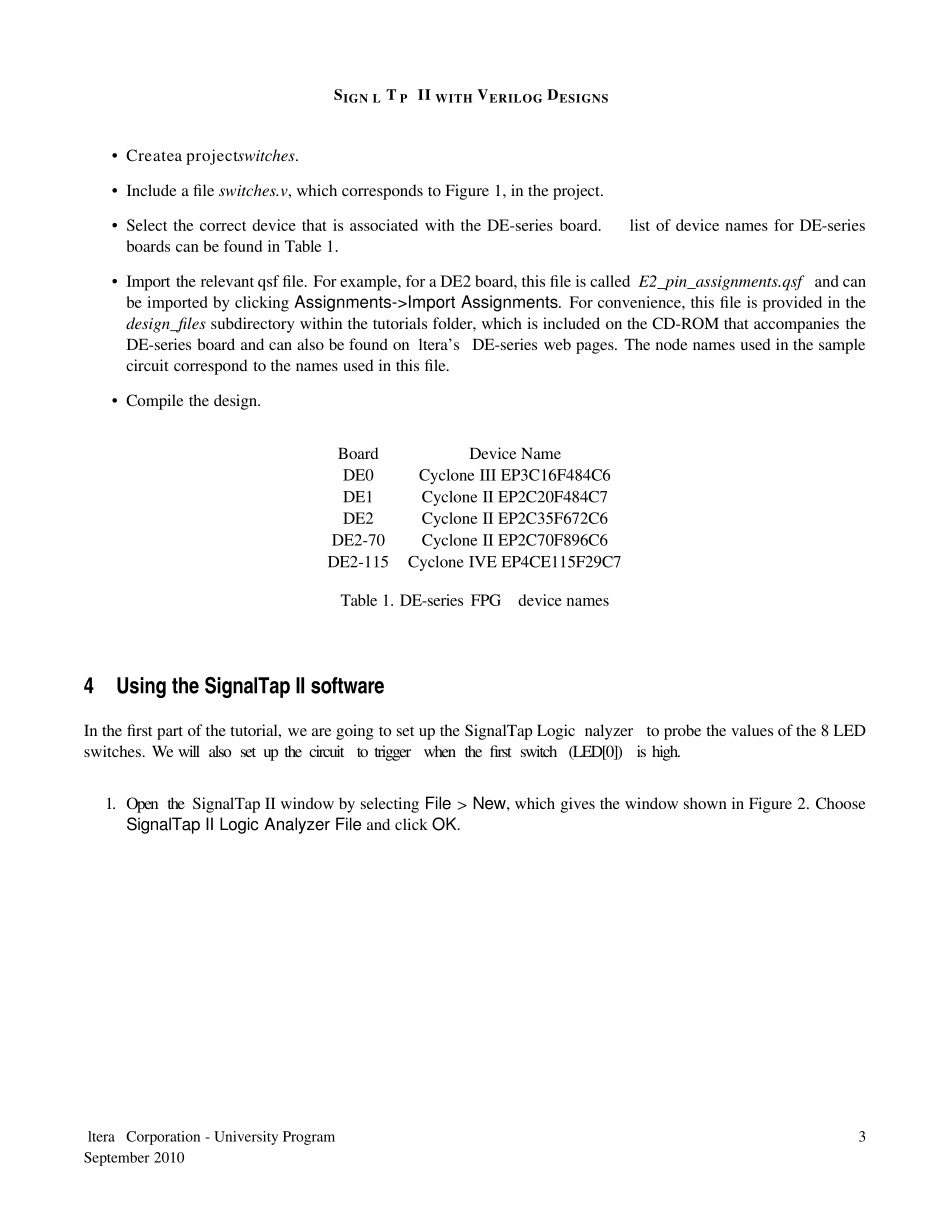

Contents:•Example Circuit•Using the SignalTap II Logic Analyzer•Probing the Design Using SignalTap•Advanced Trigger Options•Sample Depth and Buffer Acquisition ModesAltera Corporation - University ProgramSeptember 20101SIGNAL TAP II WITH VERILOG DESIGNS2BackgroundQuartus® II software includes a system level debugging tool called SignalTap II that can be used to capture anddisplay signals in real time in any FPGA design

Doing this tutorial, the reader will learn about:• Probing signals u