第二章 DDR SDRAM 的原理和时序 DDR SDRAM 全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”

DDR SDRAM 在原有的 SDRAM 的基础上改进而来

也正因为如此,DDR 能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流

由于 SDRAM 的结构与操作在前一章已有详细阐述,所以本文只着重讲讲 DDR 的原理和 DDR SDRAM 相对于传统 SDRAM(又称SDR SDRAM)的不同

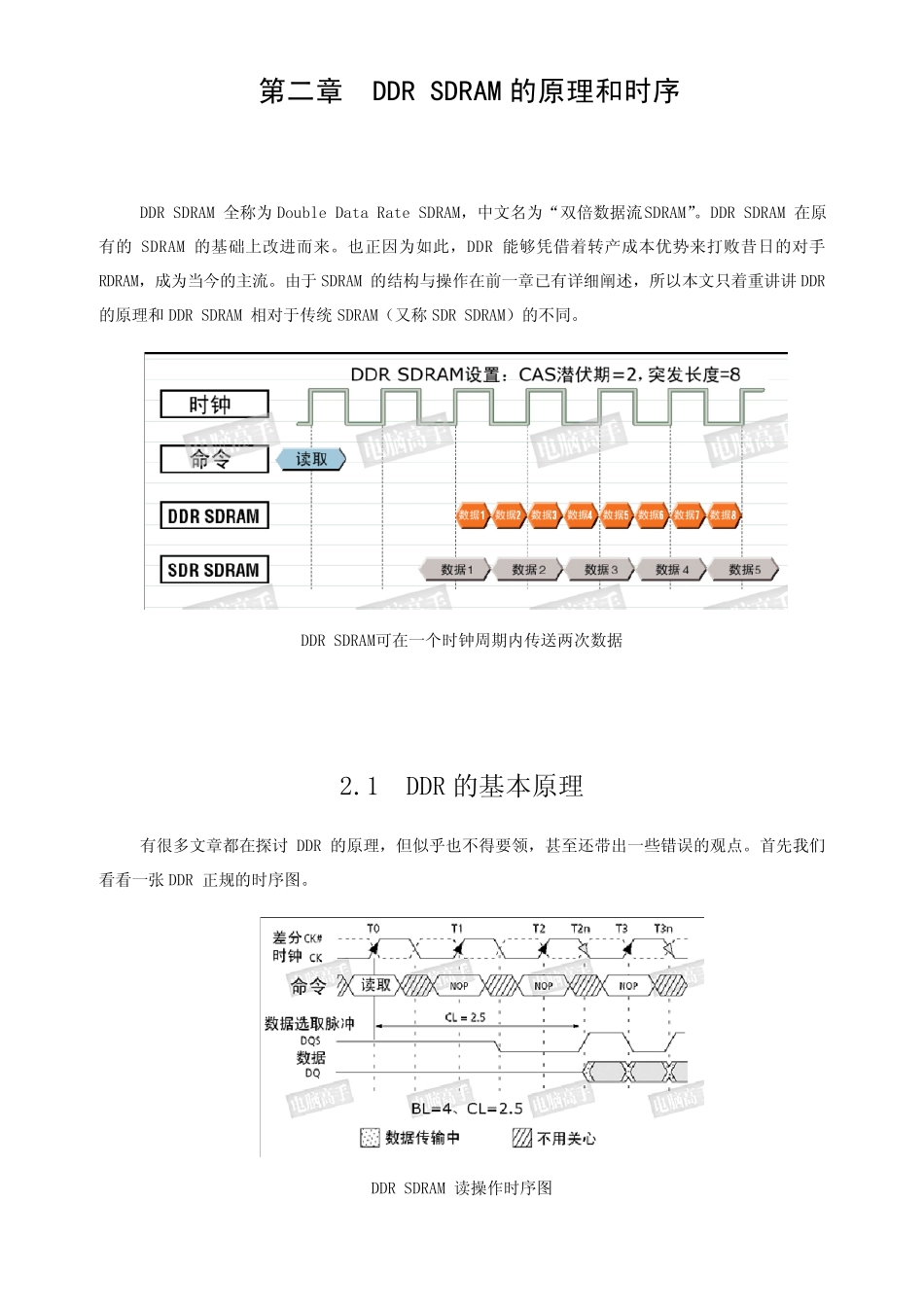

DDR SDRAM可在一个时钟周期内传送两次数据 2

1 DDR 的基本原理 有很多文章都在探讨 DDR 的原理,但似乎也不得要领,甚至还带出一些错误的观点

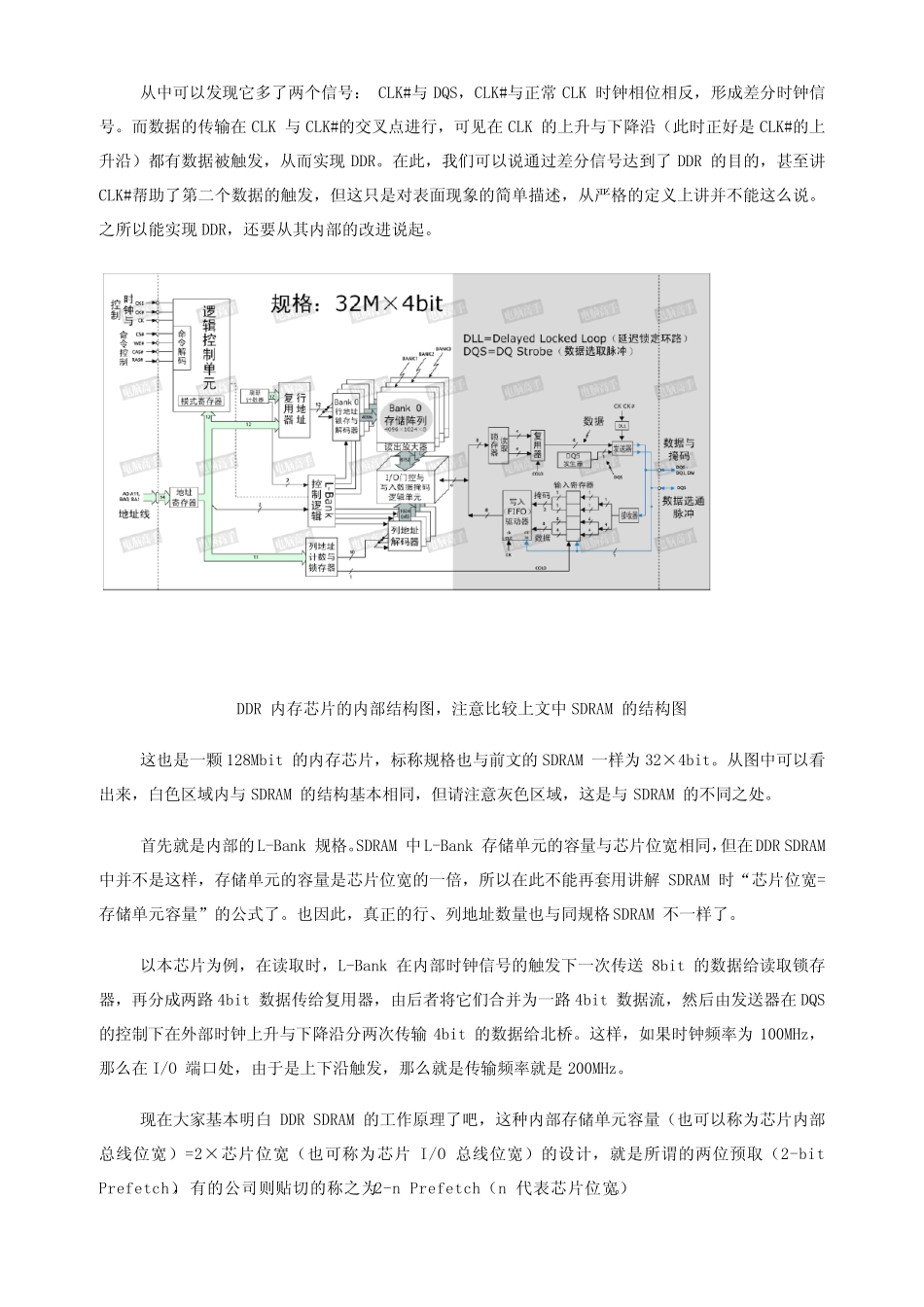

首先我们看看一张 DDR 正规的时序图

DDR SDRAM 读操作时序图 从中可以发现它多了两个信号: CLK#与DQS,CLK#与正常CLK 时钟相位相反,形成差分时钟信号

而数据的传输在CLK 与CLK#的交叉点进行,可见在CLK 的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现DDR

在此,我们可以说通过差分信号达到了DDR 的目的,甚至讲CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说

之所以能实现DDR,还要从其内部的改进说起

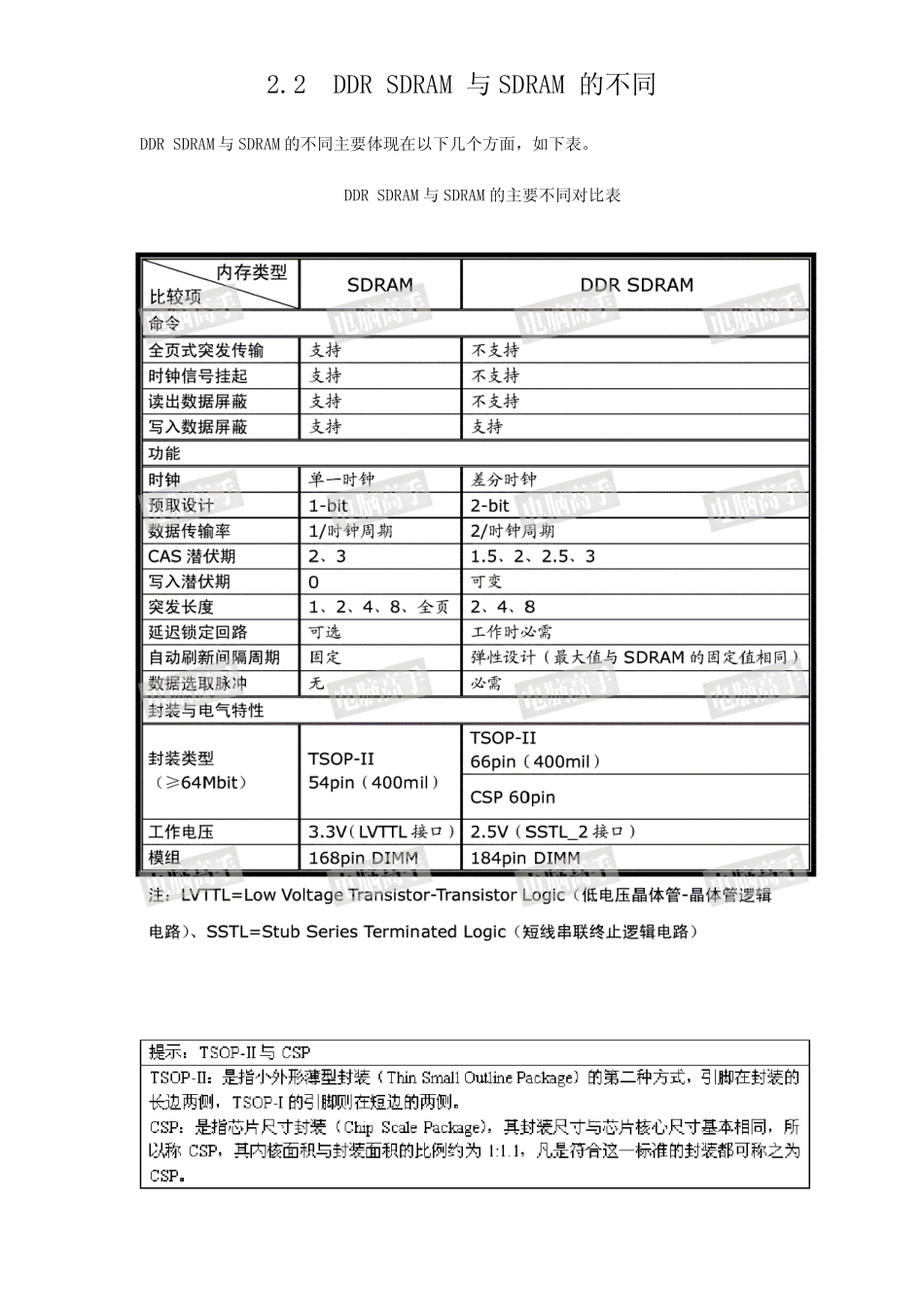

DDR 内存芯片的内部结构图,注意比较上文中SDRAM 的结构图 这也是一颗128Mbit 的内存芯片,标称规格也与前文的SDRAM 一样为32×4bit

从图中可以看出来,白色区域内与SDRAM 的结构基本相同,但请注意灰色区域,这是与SDRAM 的不同之处

首先就是内部的L-Bank 规格

SDRAM 中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM 中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解SDRAM 时“芯片位