第3节 基于System Generator的DSP系统设计 [基于System Generator的DSP系统开发技术] 第3节 基于System Generator的DSP系统设计 7

1 System Generator快速入门 本节旨在给出System Generator设计的整体轮廓,避免一上来就详细介绍各种基本操作,让读者从宏观上把握,在后续章节的阅读中不会一叶障目

1.Xilinx Blockset库的基本介绍 System Generator和 Simulink是无缝链接的,可以在MATLAB标准工具栏中直接启动,如图 8-9所示

这些模块都根据其功能划分为不同的库,为了易于使用,又在某些库中添加了部分有广泛应用的模块,所有的模块都按字母顺序排列在Xilinx Index库中

读者需要注意的是:在Simulink环境中,只有通过 Xilinx模块搭建的系统才能保证硬件可实现,其地位类似于HDL语言中的可综合语句

图 7-9 Xilinx DSP模块集 从设计流程中可以看出,熟悉 Xilinx DSP基本模块库是设计流程中的关键环节,只有掌握了基本模块的特性和功能,才能更好地实现算法

由 Xilinx模块库和 System Generator一起,可生成 Xilinx可编程器件的最优逻辑,这属于最低层的设计模块,地位等效于IP Core,共有 90多个

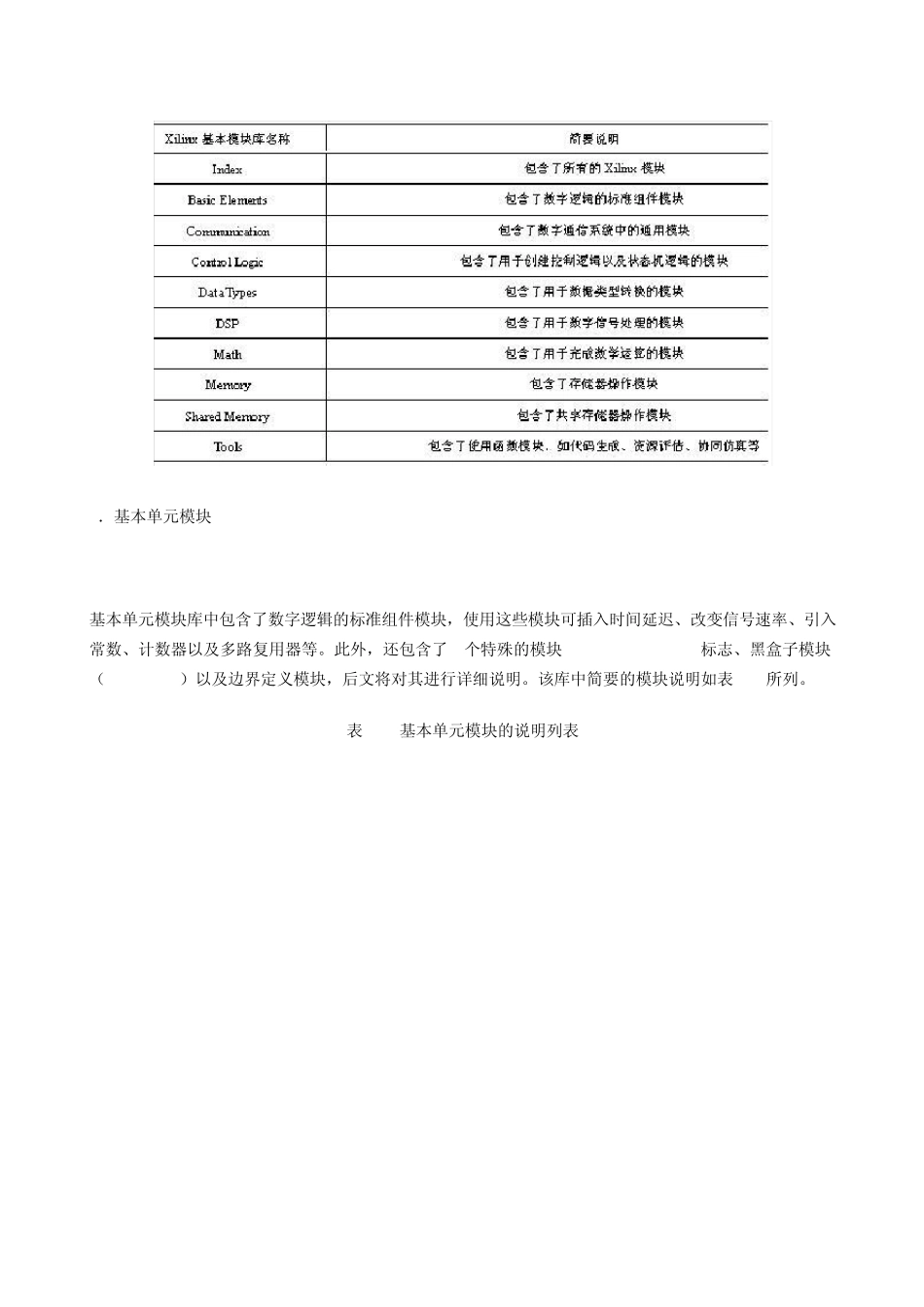

Xilinx模块库简要说明如表 7-1所列

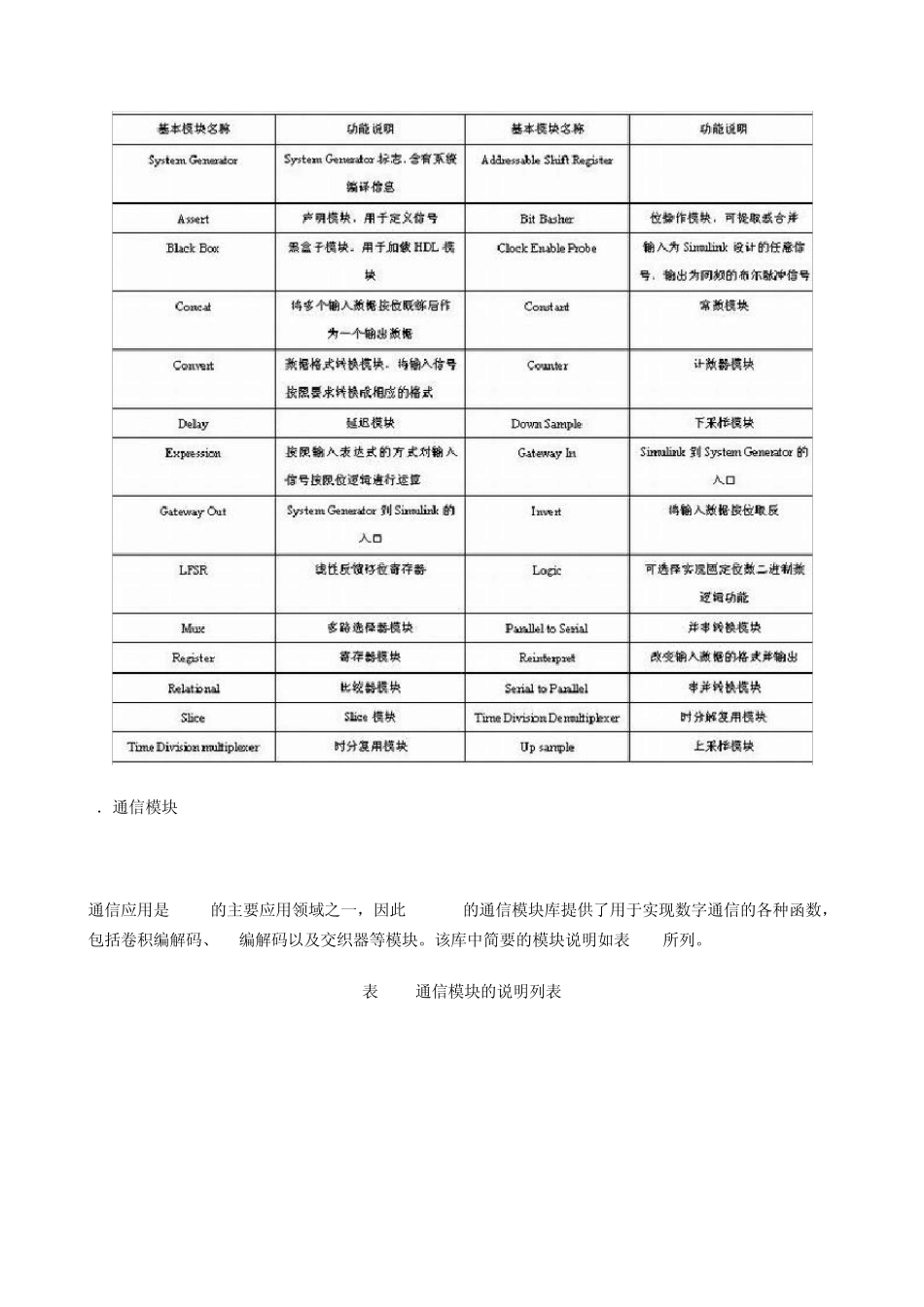

表 7-1 System Generator库的简要说明 1.基本单元模块 基本单元模块库中包含了数字逻辑的标准组件模块,使用这些模块可插入时间延迟、改变信号速率、引入常数、计数器以及多路复用器等

此外,还包含了3个特殊的模块System Generator标志、黑盒子模块(Black Box)以及边界定义模块,后文将对其进行详细说明

该库中简要的模块说明如