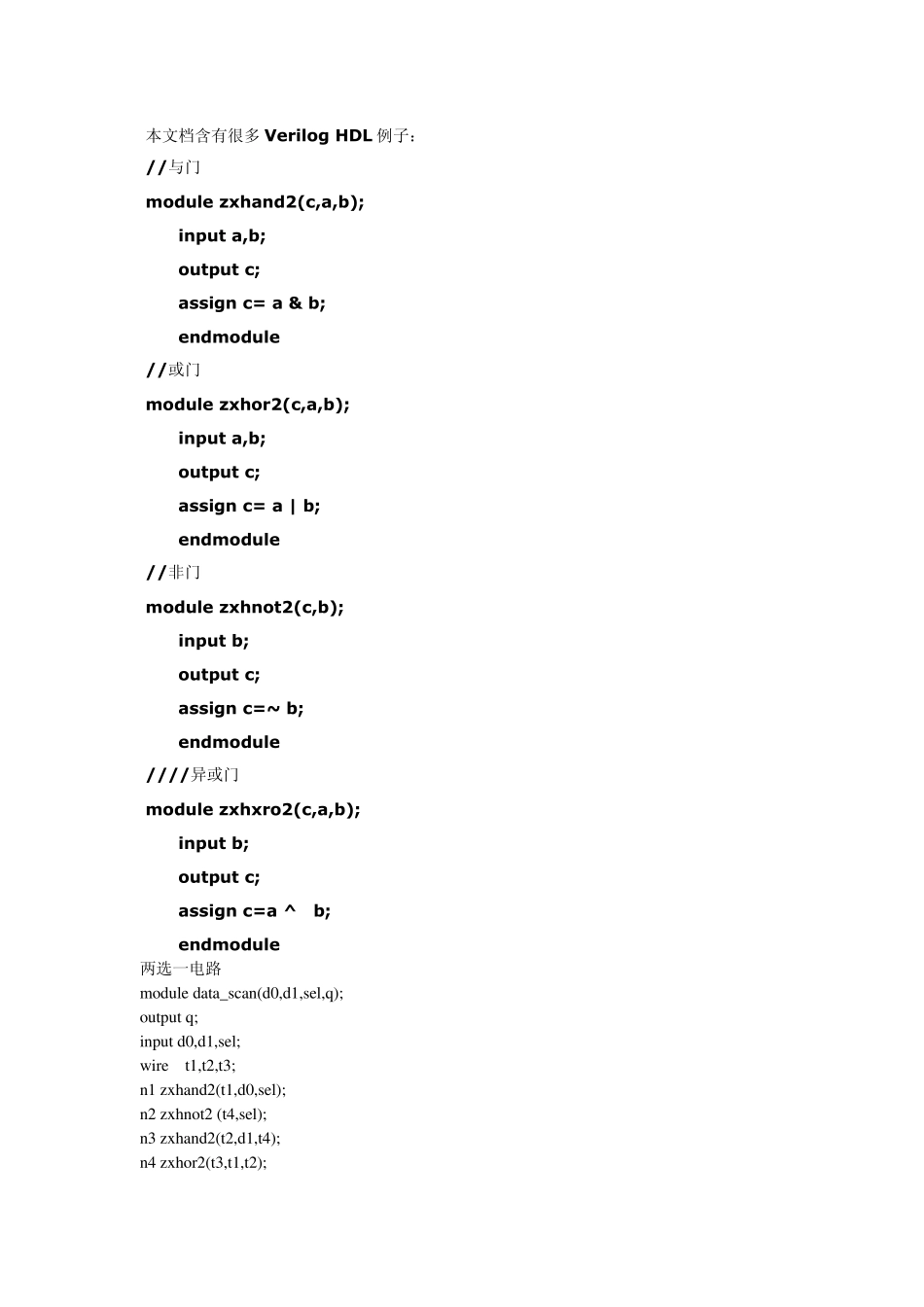

本文档含有很多Verilog HDL 例子: //与门 module zxhand2(c,a,b); input a,b; output c; assign c= a & b; endmodule //或门 module zxhor2(c,a,b); input a,b; output c; assign c= a | b; endmodule //非门 module zxhnot2(c,b); input b; output c; assign c=~ b; endmodule ////异或门 module zxhxro2(c,a,b); input b; output c; assign c=a ^ b; endmodule 两选一电路 module data_scan(d0,d1,sel,q); output q; input d0,d1,sel; wire t1,t2,t3; n1 zxhand2(t1,d0,sel); n2 zxhnot2 (t4,sel); n3 zxhand2(t2,d1,t4); n4 zxhor2(t3,t1,t2); assign q=t1; endmodu le v erilog HDL 实例(一) 练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法

这是一个可综合的数据比较器,很容易看出它的功能是比较数据 a 与数据 b,如果两个数据相同,则给出结果 1,否则给出结果 0

在 Verilog HDL 中,描述组合逻辑时常使用 assign 结构

注意equal=(a==b)

1:0,这是一种在组合逻辑实现分支判断时常使用的格式

模块源代码: //--------------- compare

v ----------------- module compare(equal,a,b); input a,b; out