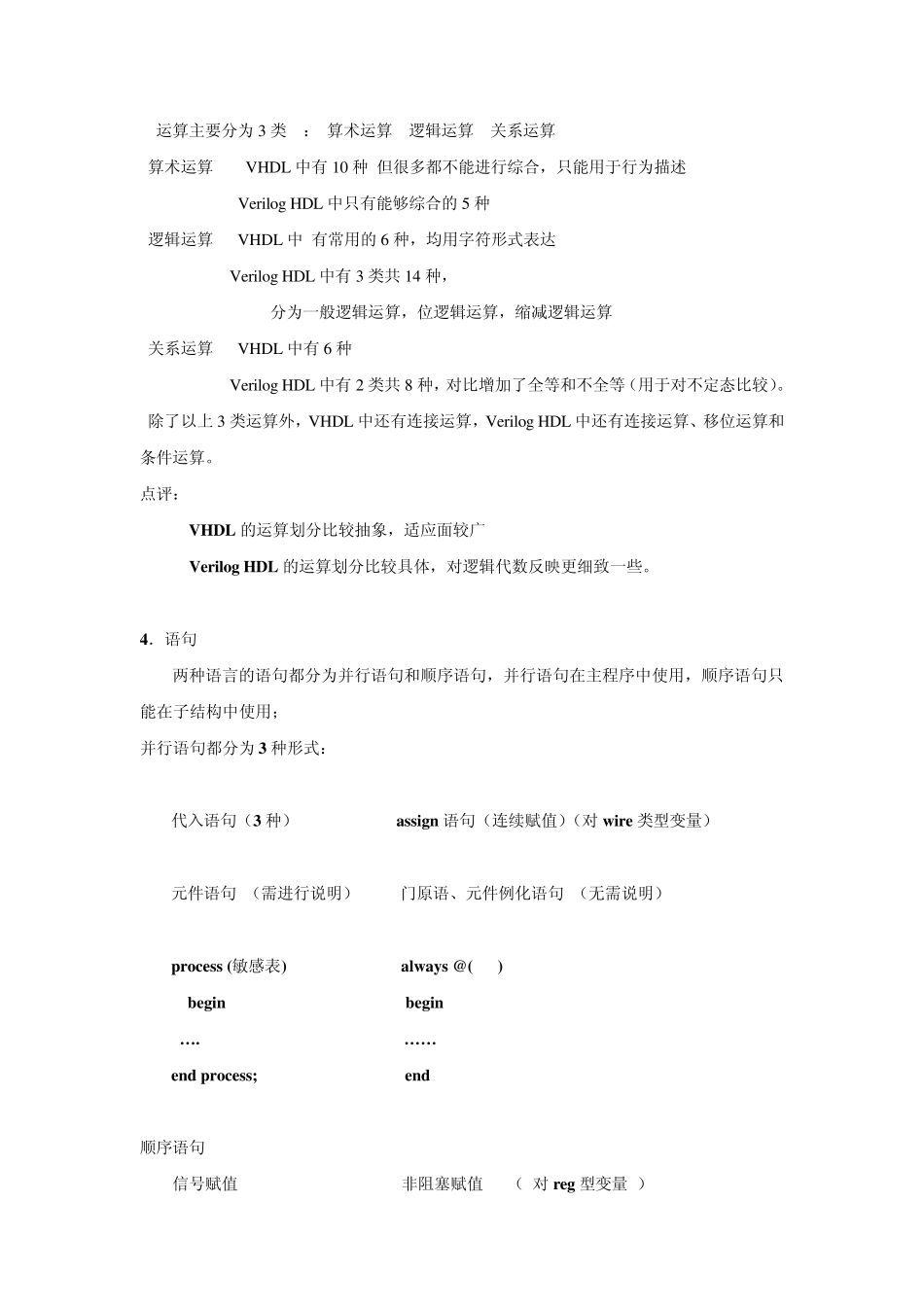

VHDL 与 Verilog HDL 的对比 1.整体结构 VHDL Verilog HDL entity 实体名 is module 模块名(端口列表) port(端口说明 ) 输入/输出端口说明 end architecture 结构体名 of 实体名 is 说明部分; 变量类型说明; begin 代入语句; assign 语句 (连续赋值语句); 元件语句; 元件例化语句; 进程语句; always @ 块语句; end 结构体名; endmodule 点评: 两者结构基本相似,并行语句的种类也类似; VHDL 语言需要进行大量说明,程序通常比较长; Verilog HDL 通常不进行说明,或只进行非常简短的说明,程序比较简短

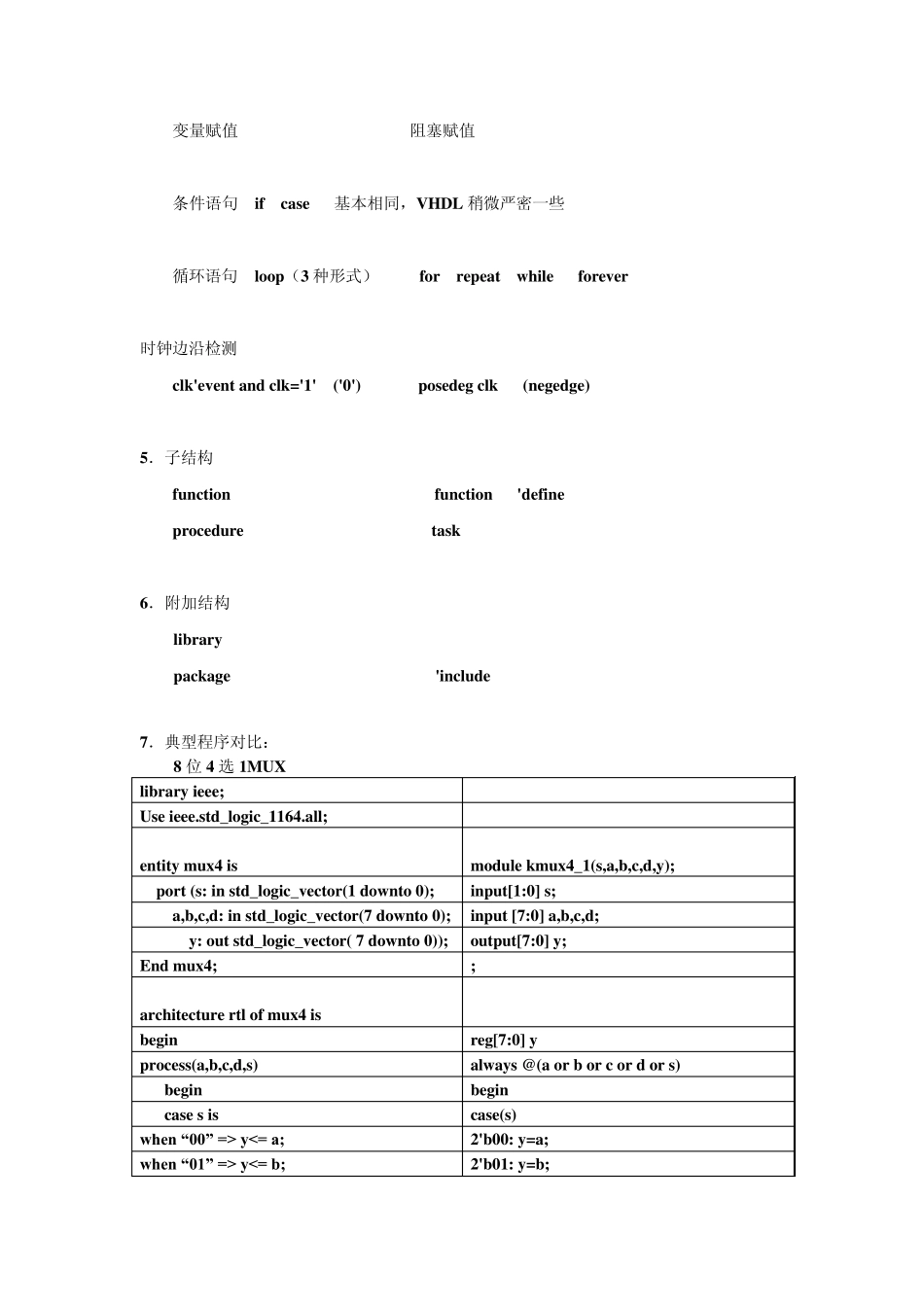

2.数据对象及类型 VHDL 常量 信号 变量 9 种预定义类型 各类用户定义类型 可描述各类不同的量 必须进行类型说明 运算时必须考虑类型的一致性和适用性 Verilog HDL 常量: 数量,参量 变量:网络型 寄存器型 类型种类少 运算时所受的约束少 3.运算符号 运算主要分为3 类 : 算术运算 逻辑运算 关系运算 算术运算 VHDL 中有10 种 但很多都不能进行综合,只能用于行为描述 Verilog HDL 中只有能够综合的5 种 逻辑运算 VHDL 中 有常用的6 种,均用字符形式表达 Verilog HDL 中有3 类共14 种, 分为一般逻辑运算,位逻辑运算,缩减逻辑运算 关系运算 VHDL 中有6 种 Verilog HDL 中有2 类共8 种,对比增加了全等和不全等(用于对不定态比较)

除了以上3 类运算外,VHDL 中还有连接运算,Verilog HDL 中还有连接运算、移位运算和条件运算

点评: VHDL 的运算划分比较抽象,适应面较广 Verilog HDL 的运算划分比较具体,对逻辑代数反映更细致一些