精选组合逻辑电路设计实验报告1

实验题目组合电路逻辑设计一:① 用卡诺图设计 8421 码转换为格雷码的转换电路

② 用 74LS197 产生连续的 8421 码,并接入转换电路

③ 记录输入输出所有信号的波形

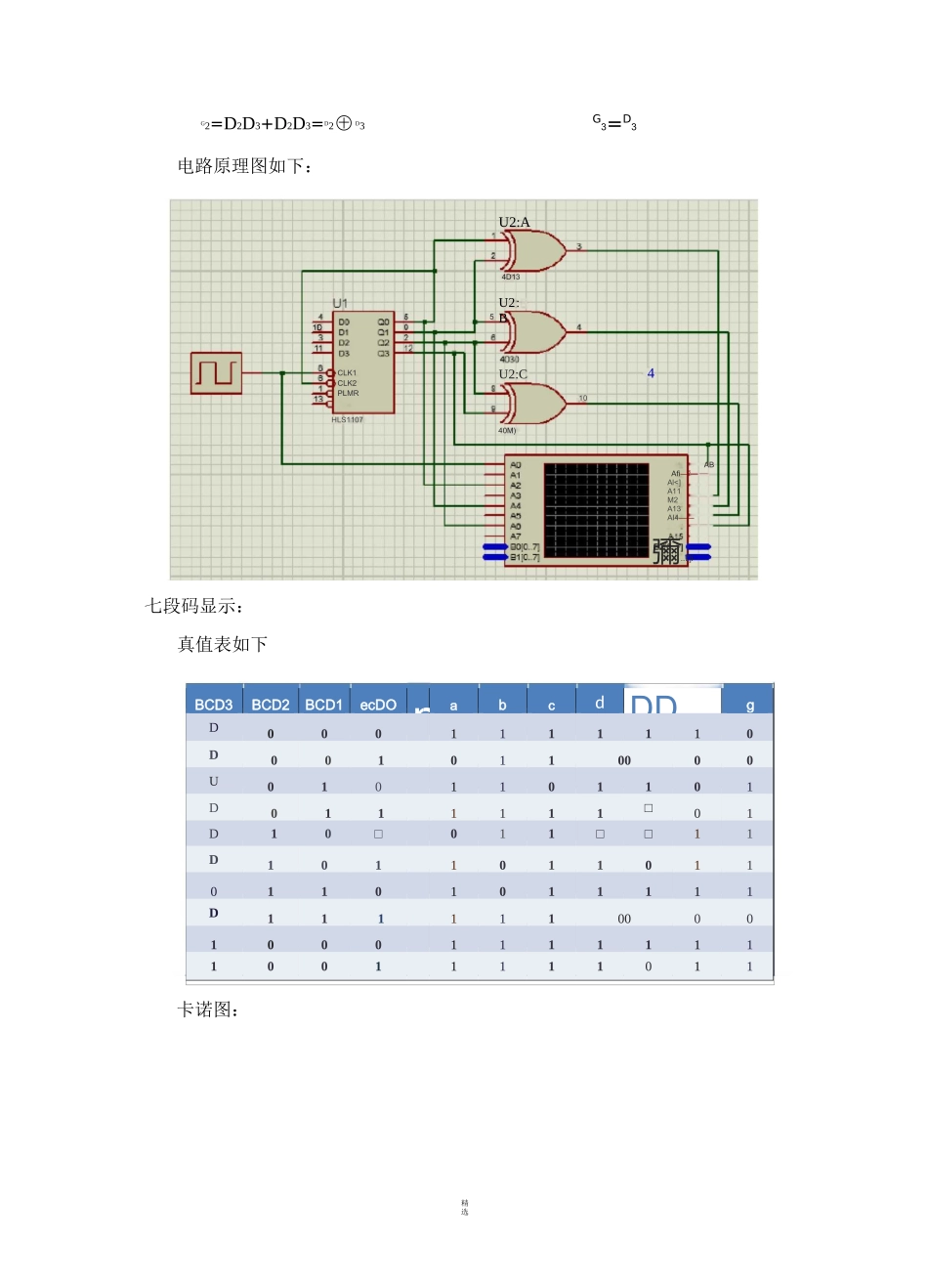

组合电路逻辑设计二:① 用卡诺图设计 BCD 码转换为显示七段码的转换电路

② 用 74LS197 产生连续的 8421 码,并接入转换电路

③ 把转换后的七段码送入共阴极数码管,记录显示的效果

实验目的(1)学习熟练运用卡诺图由真值表化简得出表达式(2)熟悉了解 74LS197 元件的性质及其使用3

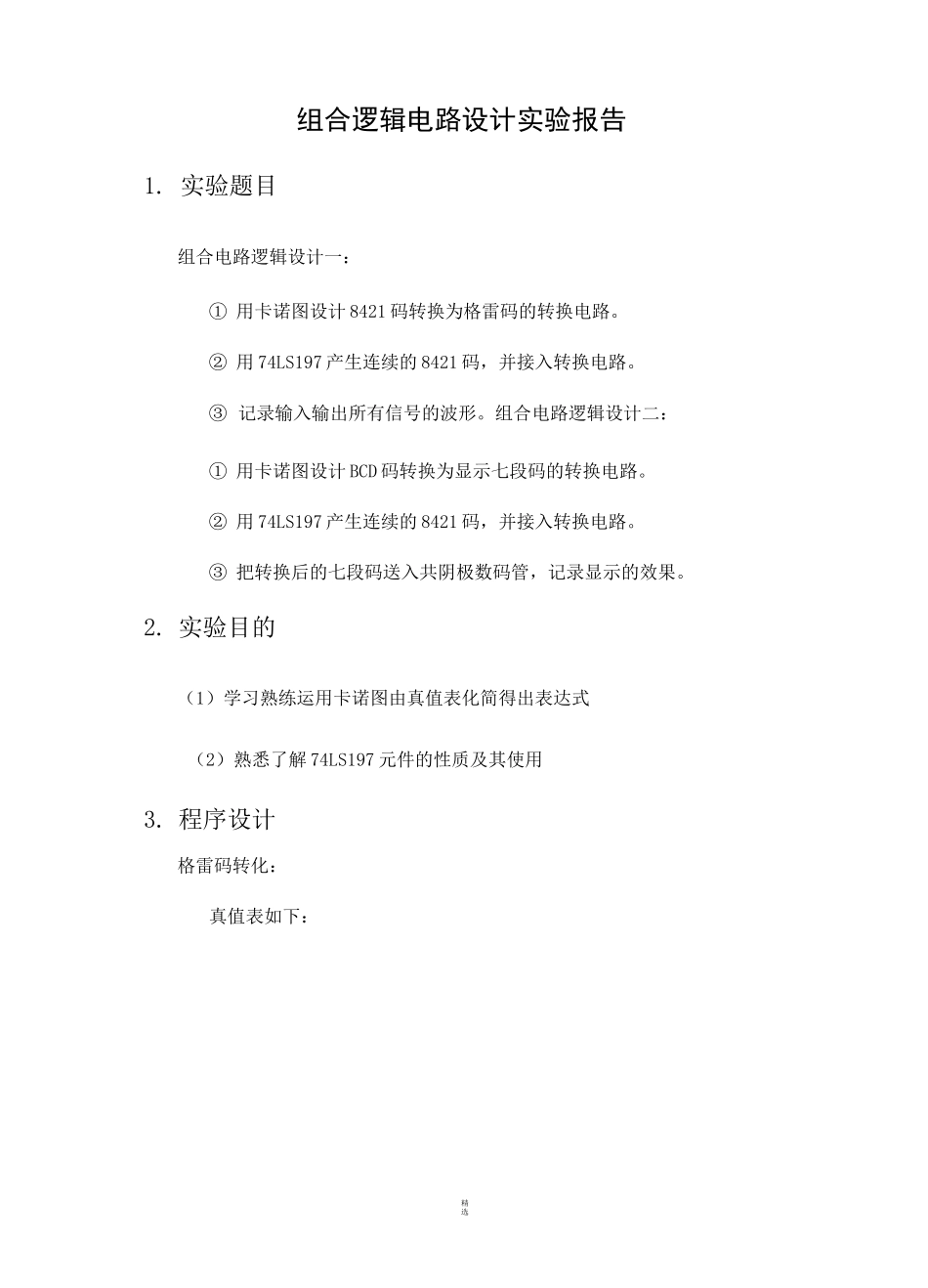

程序设计格雷码转化:真值表如下:GiGo=D0D1+D0D1=Do㊉ DiG1=D1D2+D1D2=Di㊉ D2精选G3G3Di:c[诚011110000Q P遂:010111oi0100 UDm、、0001:ii10;000■6''A遜

0■6'■i1110■6'•i i100■O'I1

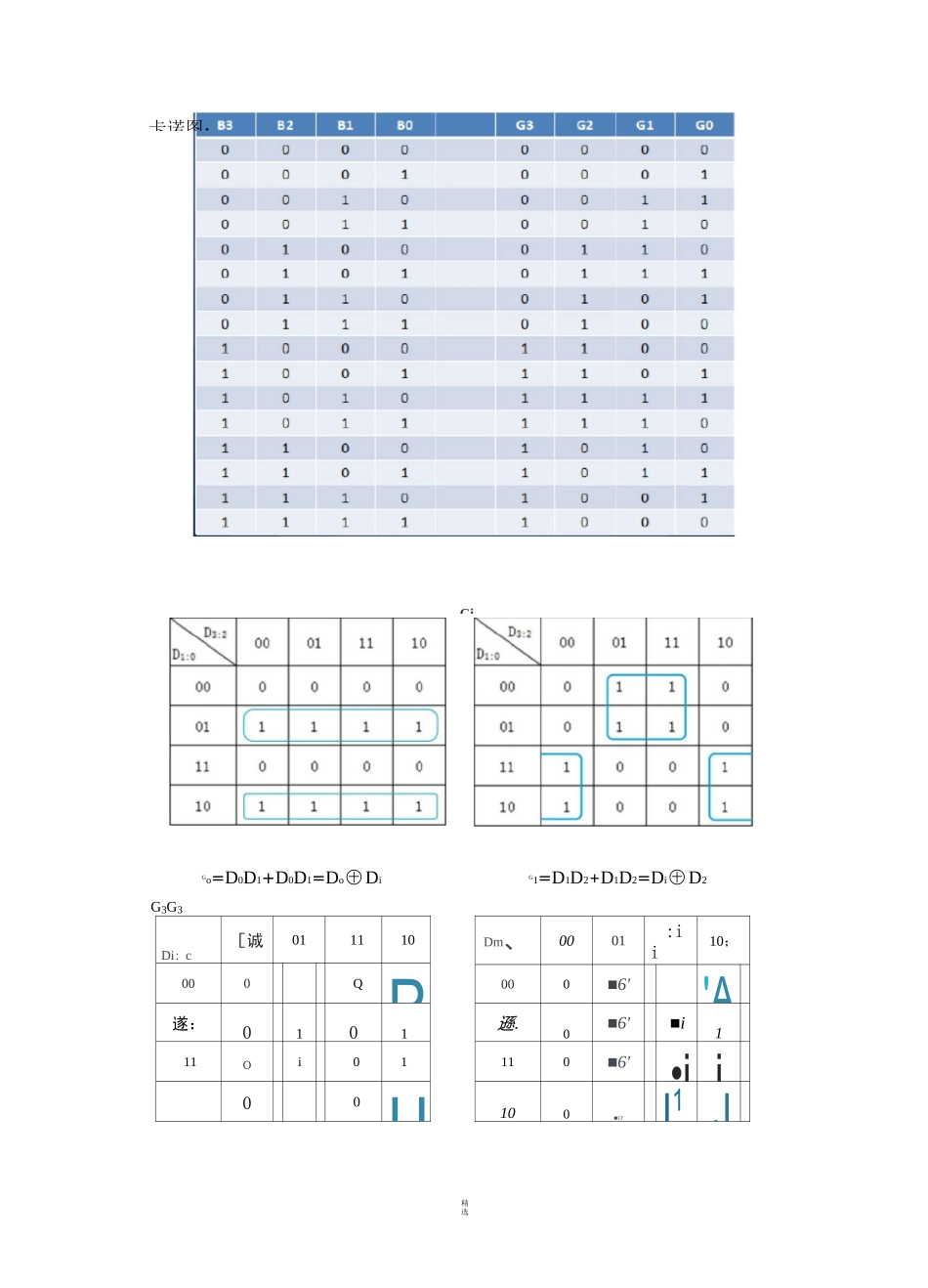

J卡诺图:精选G2=D2D3+D2D3=D2㊉ D3电路原理图如下:G3=D3U2:B51D410U2:CU2:A4D13HLS110740M)CLK1CLK2PLMRABAfi—8—Al