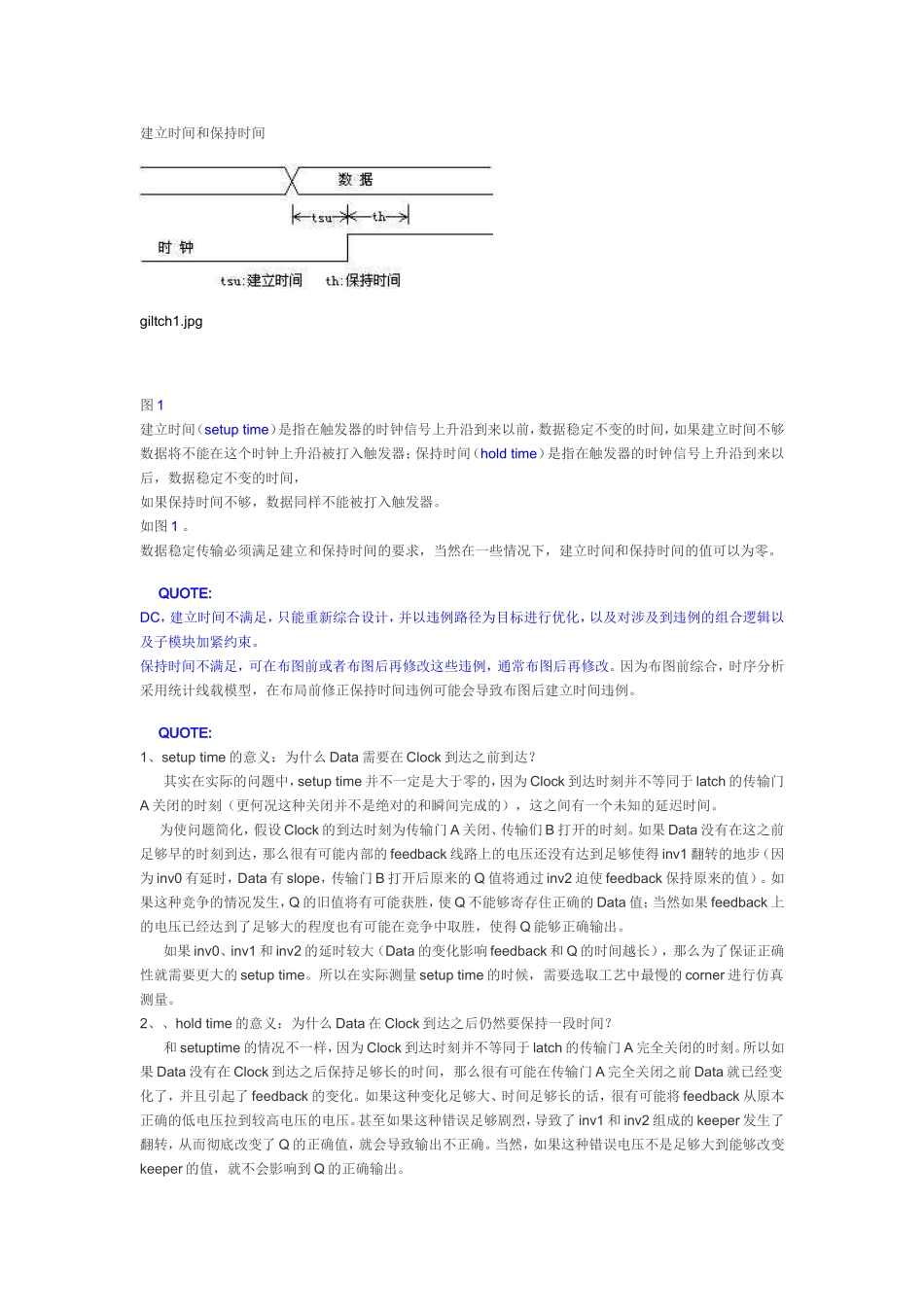

建立时间和保持时间giltch1

jpg图1建立时间(setuptime)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够数据将不能在这个时钟上升沿被打入触发器;保持时间(holdtime)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零

QUOTE:DC,建立时间不满足,只能重新综合设计,并以违例路径为目标进行优化,以及对涉及到违例的组合逻辑以及子模块加紧约束

保持时间不满足,可在布图前或者布图后再修改这些违例,通常布图后再修改

因为布图前综合,时序分析采用统计线载模型,在布局前修正保持时间违例可能会导致布图后建立时间违例

QUOTE:1、setuptime的意义:为什么Data需要在Clock到达之前到达

其实在实际的问题中,setuptime并不一定是大于零的,因为Clock到达时刻并不等同于latch的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间

为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻

如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)

如果这种竞争的情况发生,Q的旧值将有可能获胜,使Q不能够寄存住正确的Data值;当然如果feedback上的电压已经达到了足够大的程度也有可能在竞争中取胜,使得Q能够正确输出

如果inv0、inv1和inv2的延时较大(Data的变化影响feedback和Q的时间越长),那么为了保证正确性就需要