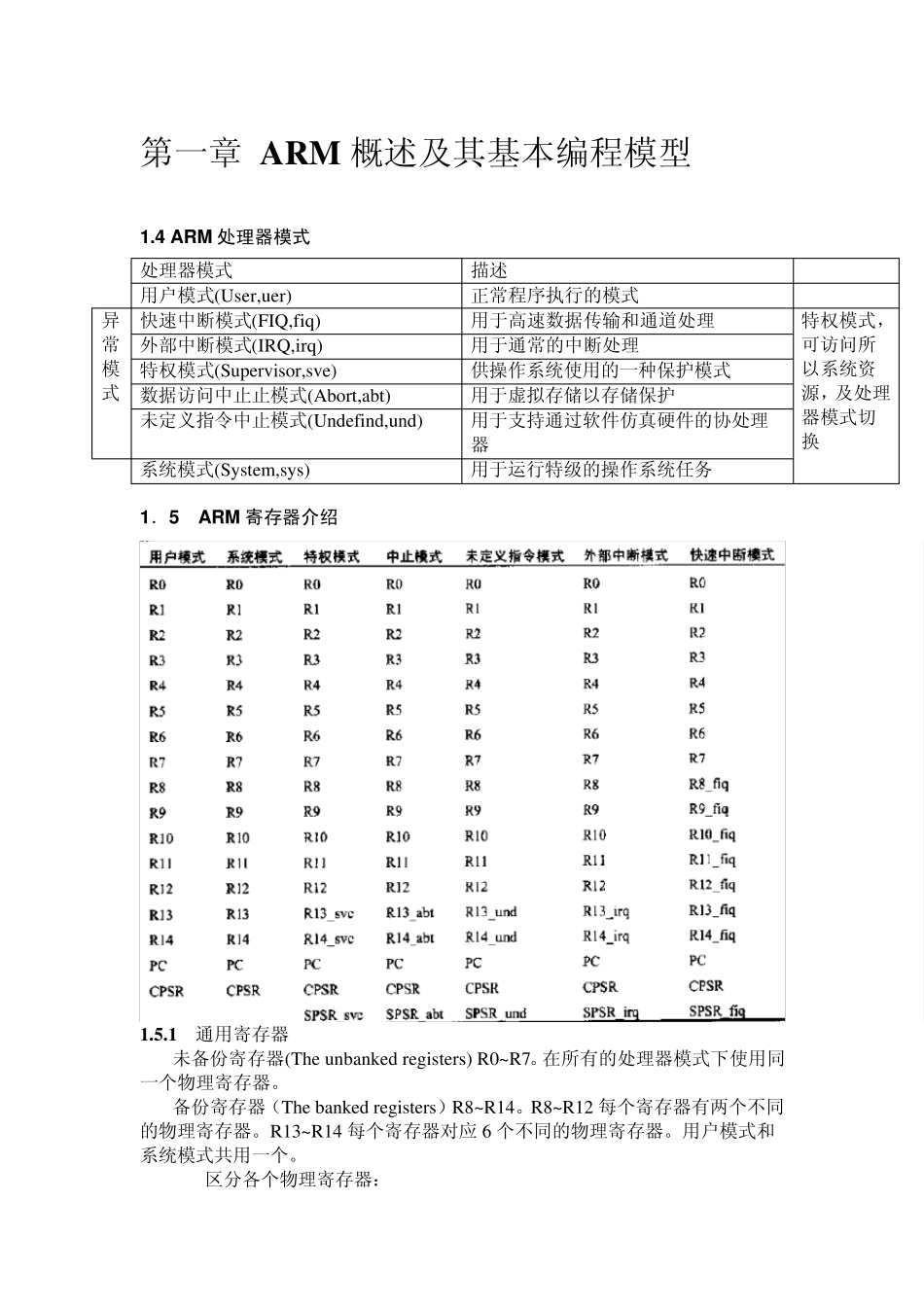

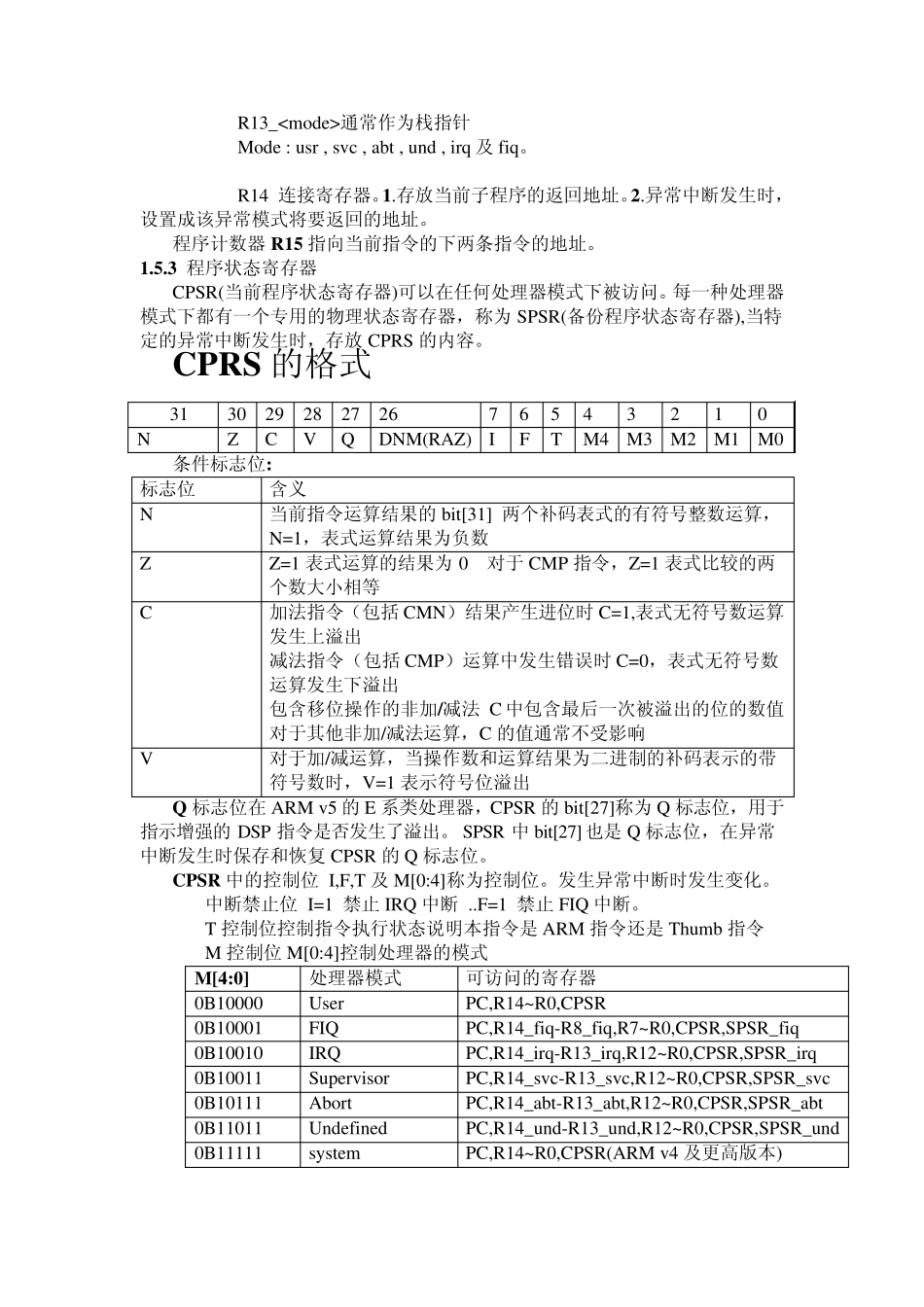

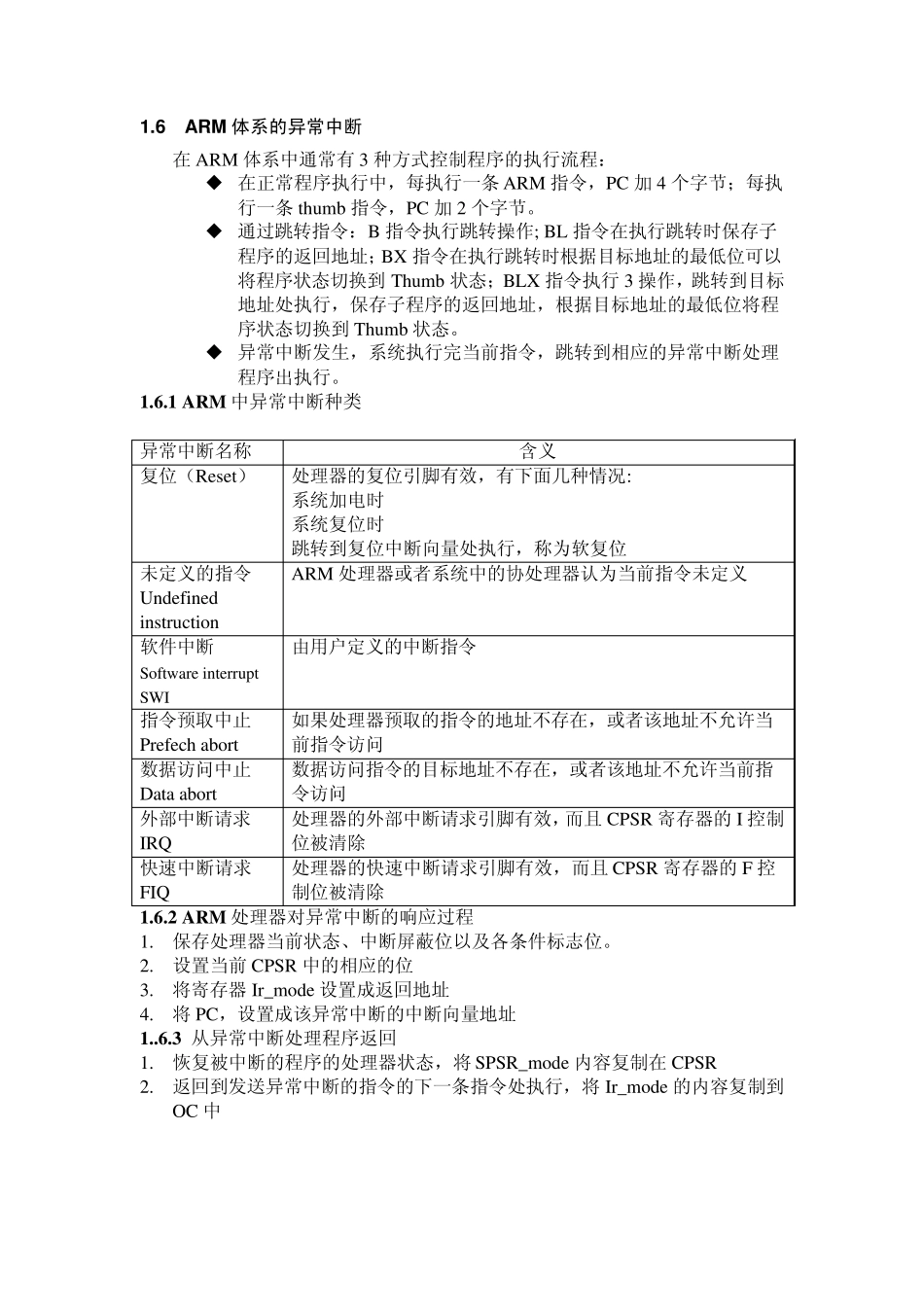

第一章 ARM 概述及其基本编程模型 1.4 ARM 处理器模式 处理器模式 描述 用户模式(User,uer) 正常程序执行的模式 异常模式 快速中断模式(FIQ,fiq) 用于高速数据传输和通道处理 特权模式,可访问所以系统资源,及处理器模式切换 外部中断模式(IRQ,irq) 用于通常的中断处理 特权模式(Supervisor,sve) 供操作系统使用的一种保护模式 数据访问中止止模式(Abort,abt) 用于虚拟存储以存储保护 未定义指令中止模式(Undefind,und) 用于支持通过软件仿真硬件的协处理器 系统模式(System,sys) 用于运行特级的操作系统任务 1.5 ARM 寄存器介绍 1.5.1 通用寄存器 未备份寄存器(The unbanked registers) R0~R7。在所有的处理器模式下使用同一个物理寄存器。 备份寄存器(The banked registers)R8~R14。R8~R12 每个寄存器有两个不同的物理寄存器。R13~R14 每个寄存器对应 6 个不同的物理寄存器。用户模式和系统模式共用一个。 区分各个物理寄存器: R13_通常作为栈指针 Mode : usr , svc , abt , und , irq 及fiq。 R14 连接寄存器。1.存放当前子程序的返回地址。2.异常中断发生时,设置成该异常模式将要返回的地址。 程序计数器 R15 指向当前指令的下两条指令的地址。 1.5.3 程序状态寄存器 CPSR(当前程序状态寄存器)可以在任何处理器模式下被访问。每一种处理器模式下都有一个专用的物理状态寄存器,称为SPSR(备份程序状态寄存器),当特定的异常中断发生时,存放 CPRS 的内容。 CPRS 的格式 31 30 29 28 27 26 7 6 5 4 3 2 1 0 N Z C V Q DNM(RAZ) I F T M4 M3 M2 M1 M0 条件标志位: 标志位 含义 N 当前指令运算结果的 bit[31] 两个补码表式的有符号整数运算,N=1,表式运算结果为负数 Z Z=1 表式运算的结果为0 对于 CMP 指令,Z=1 表式比较的两个数大小相等 C 加法指令(包括 CMN)结果产生进位时 C=1,表式无符号数运算发生上溢出 减法指令(包括 CMP)运算中发生错误时 C=0,表式无符号数运算发生下溢出 包含移位操作的非加/减法 C 中包含最后一次被溢出的位的数值 对于其他非加/减法运算,C 的值通常不受影响 V 对于加/减运算,当操作数和运算结果为二进制的补码表示的带符号数时,V=1 表示符号位溢出 Q 标志位在 ARM v5 的 E 系类处理器,CPSR 的 bit[27]称为Q 标志位,用于指示增强的 DSP 指令是否发生了...