基于Infiniium MSO9000 系列示波器的 DDR 总线测试方案 安捷伦科技中国有限公司 --- 马卓凡 概述 DDR (Double Data Rate) DRAM由于性能和价格的优势,正日益广泛的应用于计算机平台以及各种嵌入式产品设计中

DDR 规范从DDR1, DDR2 发展到DDR3,并且也发展出主要应用于移动设备领域的LPDDR (低功耗DDR)

随着总线速度的提高,信号完整性问题,互操作问题越来越被设计和测试人员关注

而由于DDR 总线复杂度高,探测困难,测试和分析也有非常大挑战

本篇文章将从DDR 总线的探测、分析、测量等方面介绍基于安捷伦MSO9000系列示波器的DDR 总线解决方案

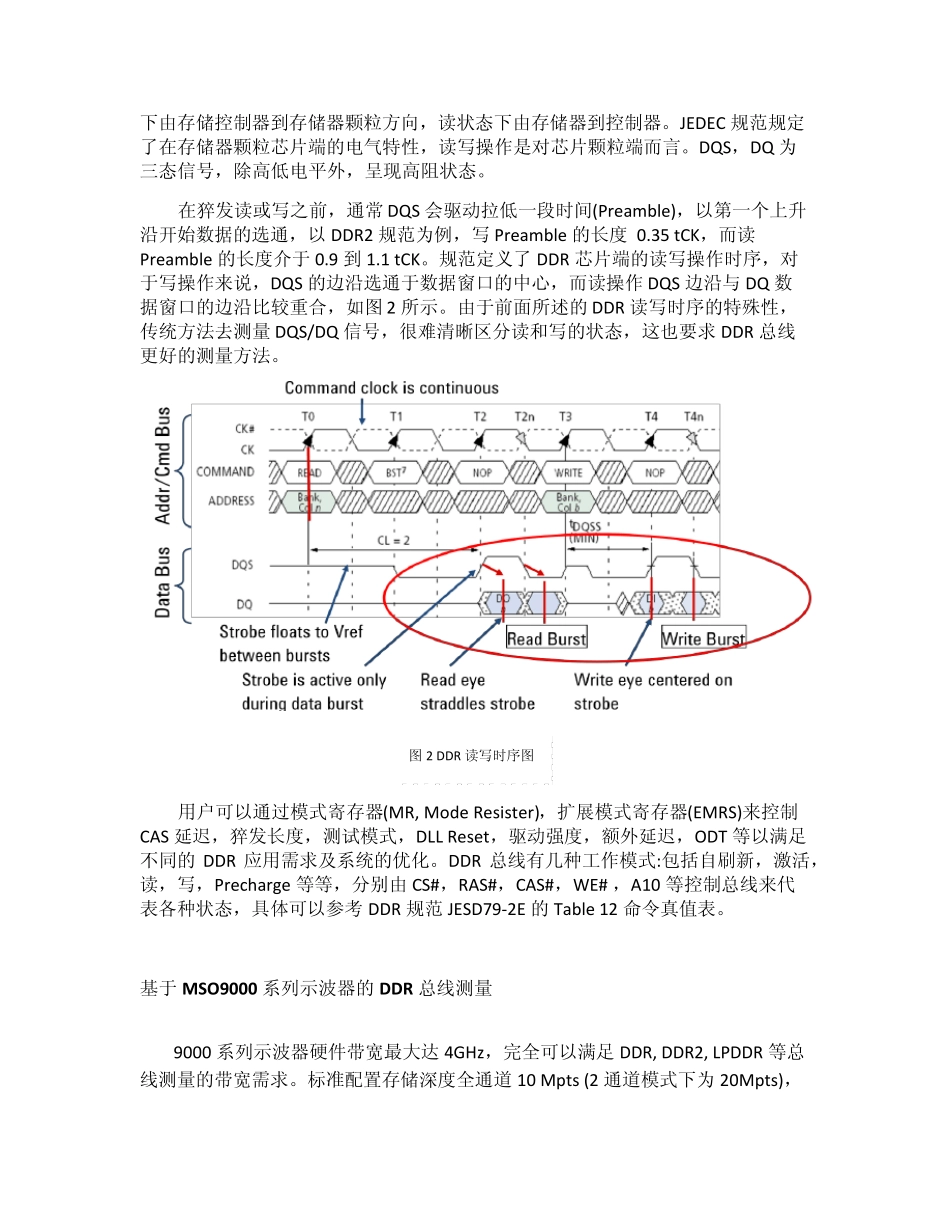

DDR 规范介绍 DDR 规范由JEDEC(电子器件工程联合会)制定,总线的电气参数由表 1 所示: 表 1 DDR 规范表格 DDR 总线包括数据 (DQ) ,时钟 (CLK) ,数据选通 (DQS, DQ Strobe) ,地址总线和控制总线等;采用双边沿传输数据的机制,源同步的总线架构:DQS 的上升/下降沿选通DQ 总线,CLK 的上升/下降沿选通地址和命令总线,如图 1 所示

其中CLK,地址/控制总线为单向传输,从存储控制器向存储器颗粒方向;DQS 和DQ 是双向的总线,写状态 DDR1 DDR2 DDR3 工作电压 2

5 V 时钟频率 100 – 200 MHz 200 – 400 MHz 400 – 800 MHz 数据传输速率 200 – 400 MT/s 400 – 800 MT/s 800 – 1600 MT/s 管脚数 184 240 240 猝发长度 2/4/8 4/8 4/8 源同步 DQS 单端 DQS 单端/差分 DQS 差分 ODT No Yes Yes 封装 TSOP/BGA BGA BGA 向下兼容