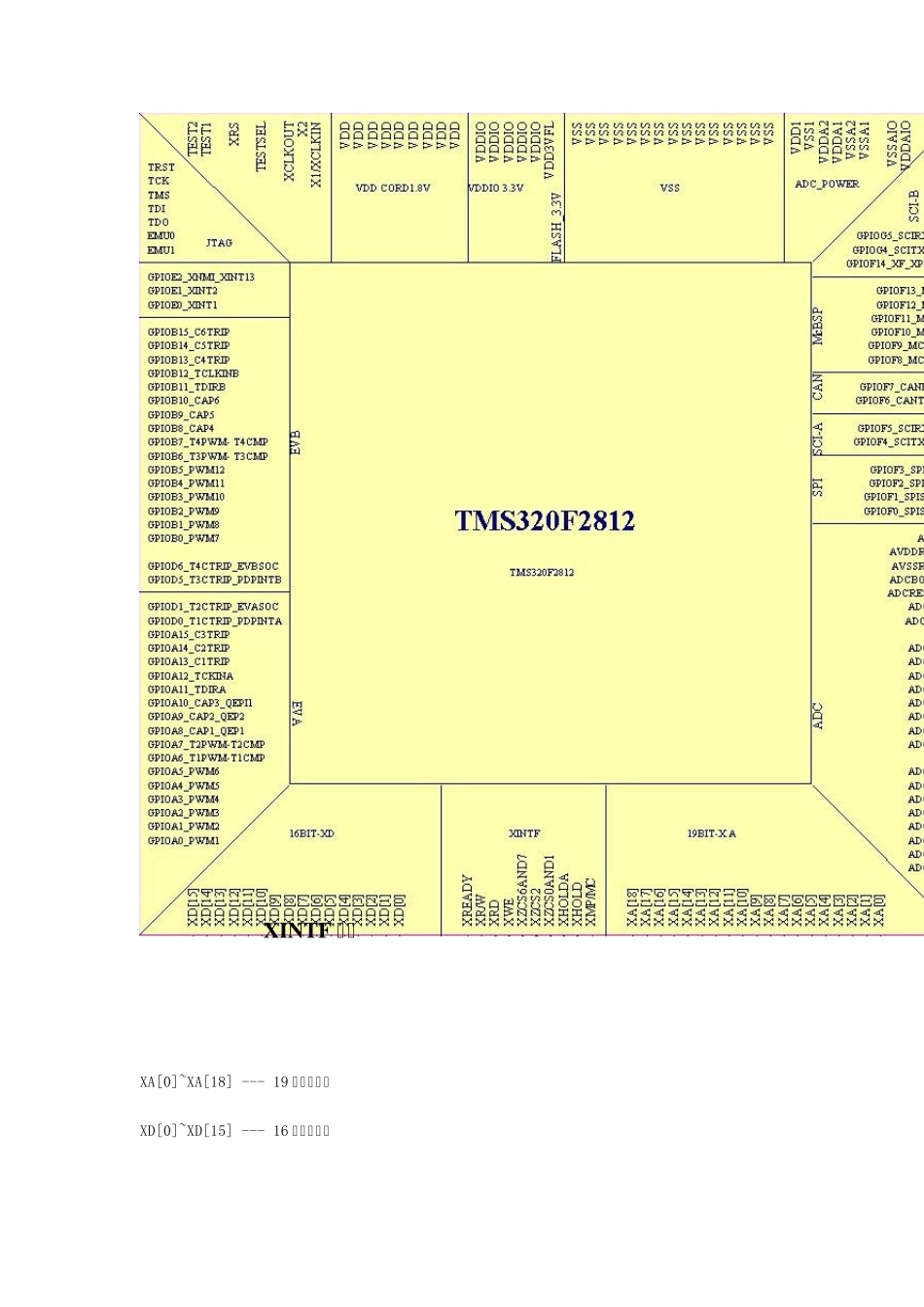

XINTF 信号 XA[0]~XA[18] --- 19 位地址总线 XD[0]~XD[15] --- 16 位数据总线 XMP/MC` --- 1 -- 微处理器模式 --- XINCNF7 有效 0 -- 微计算机模式 --- XINCNF7 无效 XHOLD` --- 外部DMA 保持请求信号

XHOLD 为低电平时请求XINTF 释放外部总线,并把所有的总线与选通端置为高阻态

当对总线的操作完成且没有即将对XINTF 进行访问时,XINTF 释放总线

此信号是异步输入并与XTIMCLK 同步 XHOLDA` --- 外部DMA 保持确认信号

当XINTF 响应XHOLD 的请求时XHOLDA 呈低电平,所有的XINTF 总线和选通端呈高阻态

XHOLD 和 XHOLDA 信号同时发出

当XHOLDA 有效(低 )时外部器件只能使用外部总线 XZCS0AND1` --- XINTF 区域O 和区域1 的片选,当访XINTF 区域0 或 1 时有效(低 ) XZCS2` --- XINTF 区域2 的片选,当访XINTF 区域2 时有效(低 ) XZCS6AND7` --- XINTF 区域6 和区域7 的片选,当访XINTF 区域6 或 7 时有效(低 ) XWE` --- 写有效

有效时为低电平

写选通信号是每个区域操作的基础,由XTIMINGX 寄存器的前一周期、当前周期和后一周期的值确定 XRD` --- 读有效

低电平读选通

读选通信号是每个区域操作的基础,由xTIMINGX 寄存器的前一周期、当前周期和后一周期的值确定

注意:XRD`和 XWE`是互斥信号 XR/W` --- 通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期 XREADY --- 数据准备输入,被置1 表示外设已为访问做好准备

XREADY 可被设置为同步或异步输入