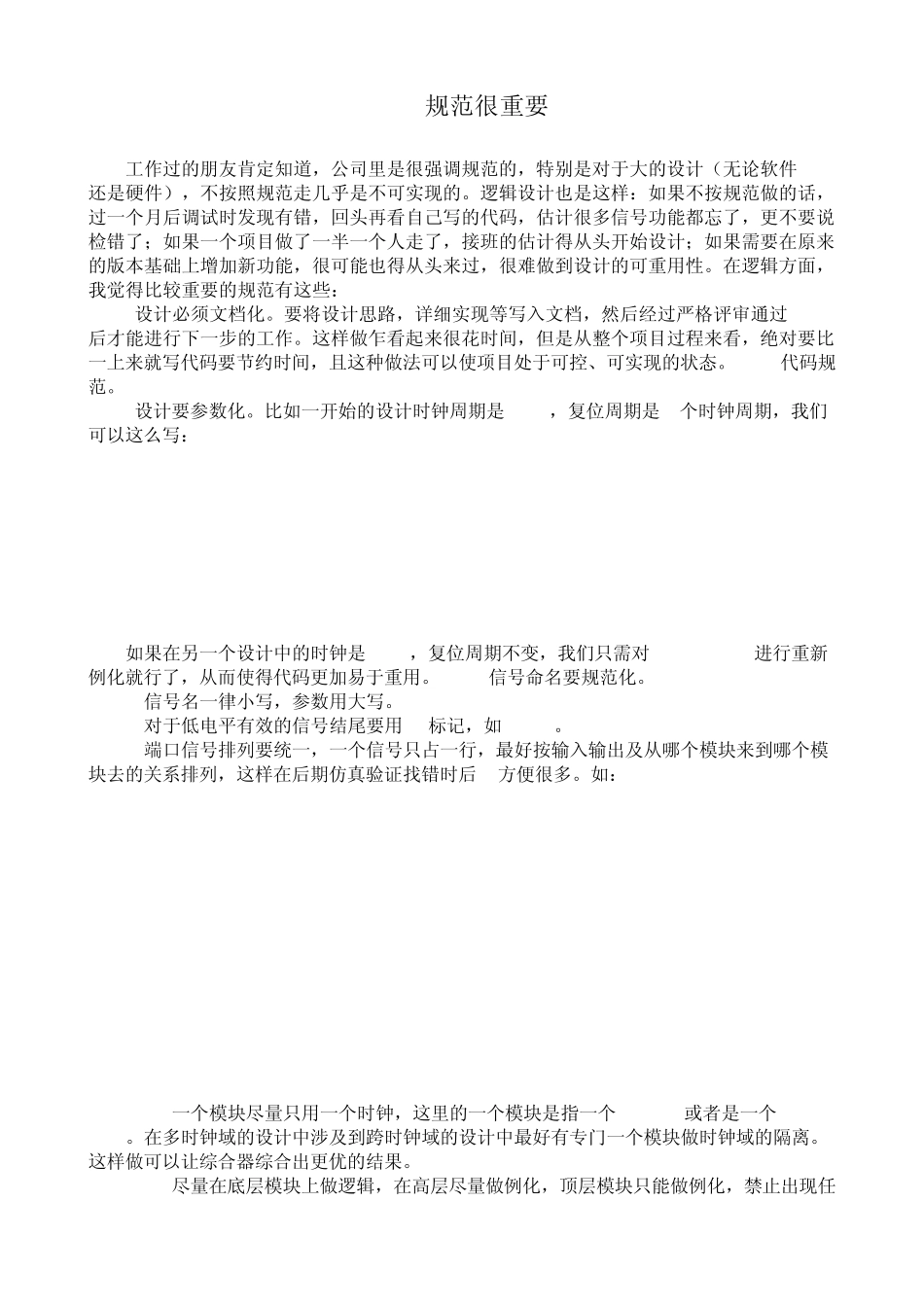

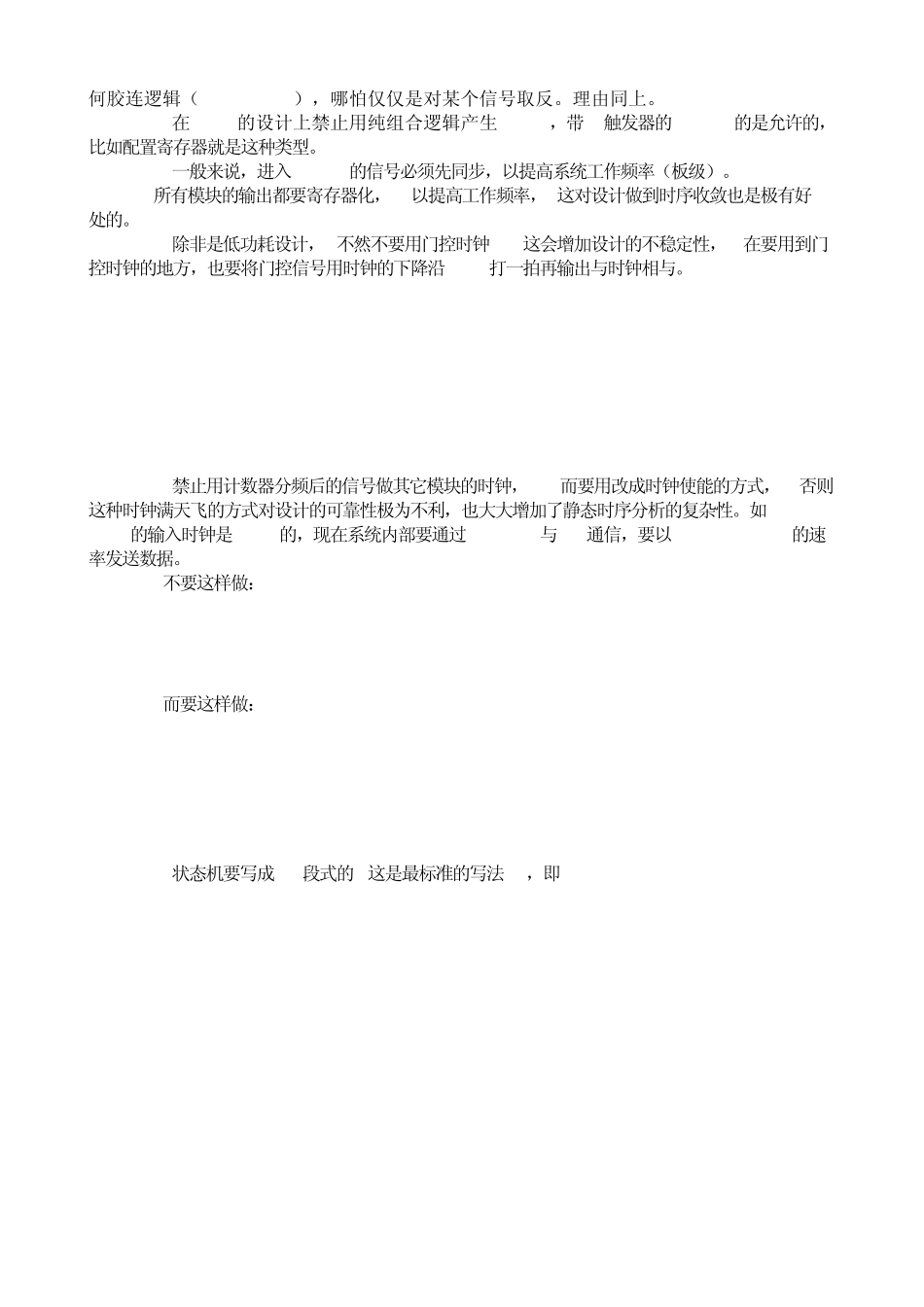

规范很重要 工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件 还是硬件),不按照规范走几乎是不可实现的。逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。在逻辑方面,我觉得比较重要的规范有这些: 1.设计必须文档化。要将设计思路,详细实现等写入文档,然后经过严格评审通过 后才能进行下一步的工作。这样做乍看起来很花时间,但是从整个项目过程来看,绝对要比一上来就写代码要节约时间,且这种做法可以使项目处于可控、可实现的状态。 2.代码规范。 a.设计要参数化。比如一开始的设计时钟周期是 30ns,复位周期是 5个时钟周期,我们可以这么写: parameter CLK_PERIOD = 30; parameter RST_MUL_TIME = 5; parameter RST_TIME = RST_MUL_TIME * CLK_PERIOD; ... rst_n = 1'b0; # RST_TIME rst_n = 1'b1; ... # CLK_PERIOD/2 clk <= ~clk; 如果在另一个设计中的时钟是 40ns,复位周期不变,我们只需对 CLK_PERIOD进行重新例化就行了,从而使得代码更加易于重用。 b.信号命名要规范化。 1) 信号名一律小写,参数用大写。 2) 对于低电平有效的信号结尾要用_n标记,如 rst_n。 3) 端口信号排列要统一,一个信号只占一行,最好按输入输出及从哪个模块来到哪个模块去的关系排列,这样在后期仿真验证找错时后 方便很多。如: module a( //input clk, rst_n, //globle signal wren, rden, avalon_din, //related to avalon bus sdi, //related to serial port input //output data_ready, avalon_dout, //related to avalon bus ... ); 4) 一个模块尽量只用一个时钟,这里的一个模块是指一个 module或者是一个 en tity。在多时钟域的设计中涉及到跨时钟域的设计中最好有专门一个模块做时钟域的隔离。这样做可以让综合器综合出更优的结果。 5) 尽量在底层模块上做逻辑,在高层尽量做例化,顶层模块只能做例化,禁止出现任何胶连逻辑(glue logic),哪怕仅仅是对某个信号取反。理由同上。 6) 在 FPGA的设计上禁止用纯组合逻辑产生 latch,带 D触发器的 latch的是允许的,比如配置寄存器就...