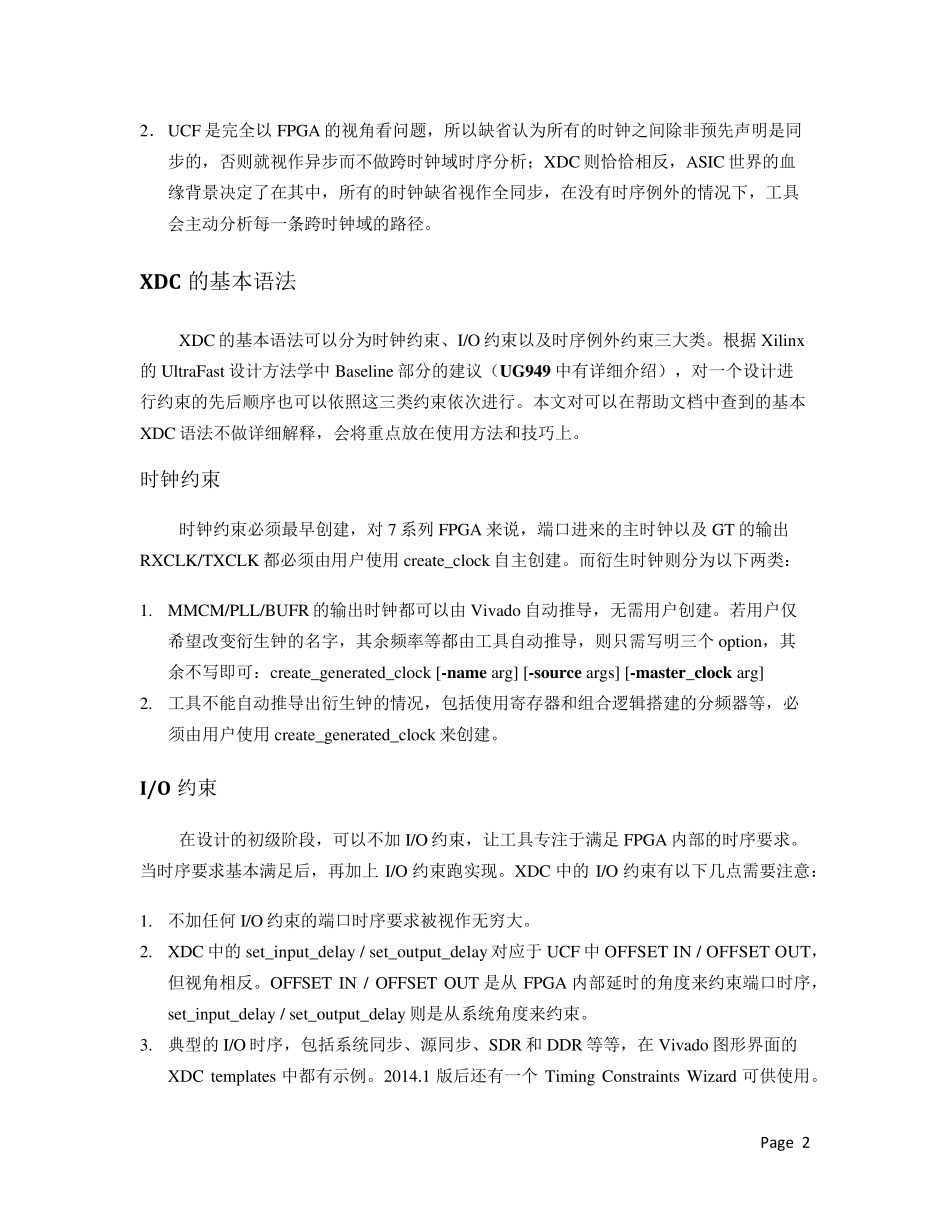

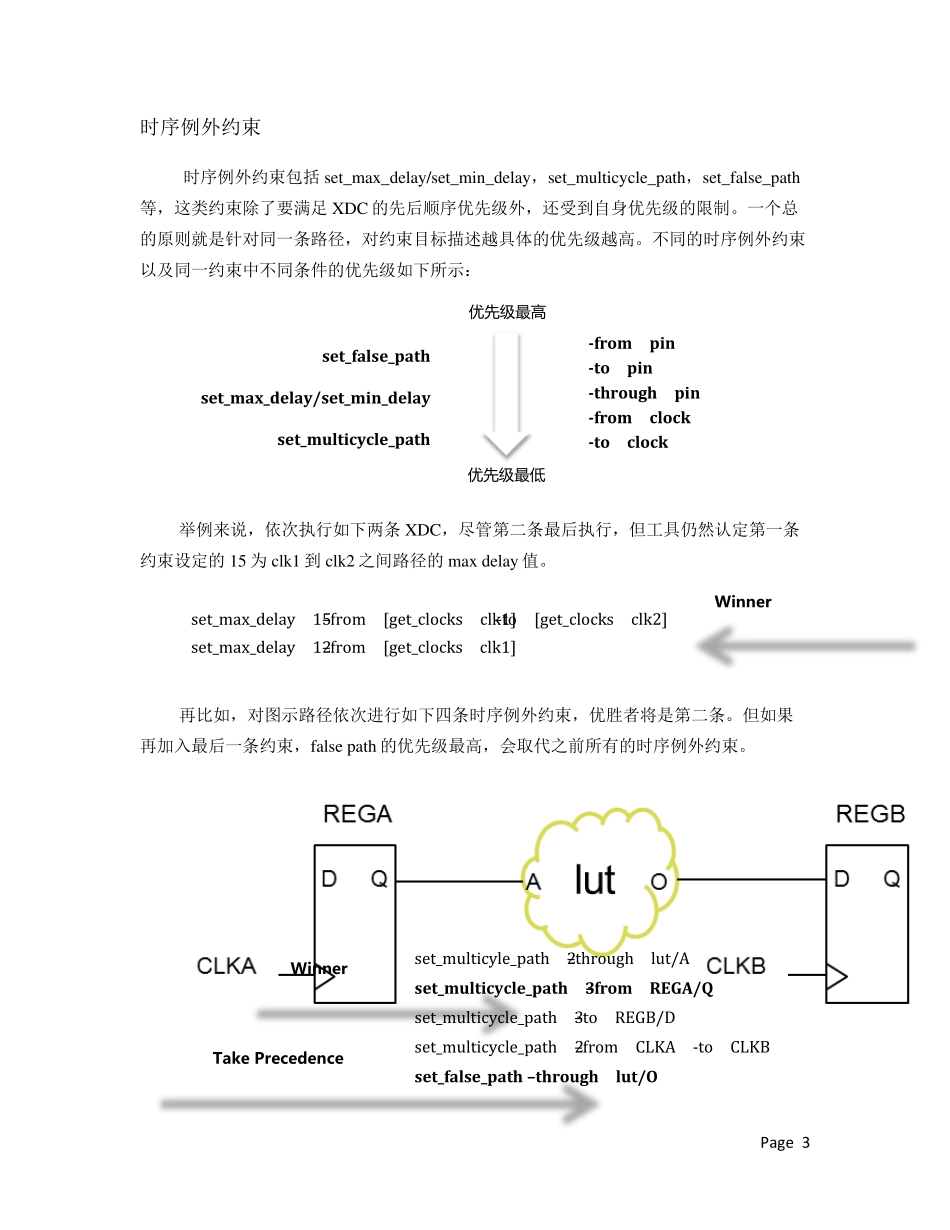

Page 1 XDC 约束技巧之时钟篇 Xilinx©的新一代设计套件Vivado 中引入了全新的约束文件XDC,在很多规则和技巧上都跟上一代产品ISE 中支持的UCF 大不相同,给使用者带来许多额外挑战。Xilinx 工具专家告诉你,其实用好XDC 很容易,只需掌握几点核心技巧,并且时刻牢记:XDC 的语法其实就是Tcl 语言。 XDC 的优势 XDC 是Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC(最早由Synopsys 公司提出,故名Synopsys Design Constraints)。所以SDC、XDC跟Vivado Tcl 的关系如下图所示。 XDC 的主要优势包括: 1. 统一了前后端约束格式,便于管理; 2. 可以像命令一样实时录入并执行; 3. 允许增量设置约束,加速调试效率; 4. 覆盖率高,可扩展性好,效率高; 5. 业界统一,兼容性好,可移植性强; XDC 在本质上就是Tcl 语言,但其仅支持基本的Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件I/O 等语法可以通过在Vivado 中source 一个 Tcl 文件的方式来补充。(对 Tcl 话题感兴趣的读者可以参考作者的另一篇文章《Tcl 在Vivado 中的应用》)XDC 与 UCF 的最主要区别有两点: 1. XDC 可以像 UCF 一样作为一个整体文件被工具读入,也可以在实现过程中被当作一个个单独的命令直接执行。这就决定了XDC 也具有 Tcl 命令的特点,即后面输入的约束在有冲突的情况下会覆盖之前输入的约束(时序例外的优先级会在下节详述)。另外,不同于UCF 是全部读入再处理的方式,在XDC 中,约束是读一条执行一条,所以先后顺序很重要,例如要设置 IO 约束之前,相对应的clock 一定要先创建好。 Page 2 2. UCF 是完全以FPGA 的视角看问题,所以缺省认为所有的时钟之间除非预先声明是同步的,否则就视作异步而不做跨时钟域时序分析;XDC 则恰恰相反,ASIC 世界的血缘背景决定了在其中,所有的时钟缺省视作全同步,在没有时序例外的情况下,工具会主动分析每一条跨时钟域的路径。 XDC 的基本语法 XDC 的基本语法可以分为时钟约束、I/O 约束以及时序例外约束三大类。根据 Xilinx的UltraFast 设计方法学中Baseline 部分的建议(UG949 中有详细介绍),对一个设计进行约束的先后顺序也可以依照这三类约束依次进行。本文对可以在帮助文档中查到的基本XDC 语法不做详细解释,会将重点放在使用方法和技巧上。 时钟约束 时钟约束必须最早创建,对 7...