2 三态门 1.基本原理 在数字系统中,常常需要把多个门电路的输出端连接在一起,比如接到数据总线上

但一般的门电路都只有两个输出状态:输出高电平状态与输出低电平状态

把这些门电路的输出端连接在一起,在某一个时刻,可能会出现一个以上的门电路的输出同时为高电平状态或者低电平状态,这样就会引起逻辑电平的不确定

使用三态门可以很好地解决这个问题

三态门电路有三个输出状态:输出高电平状态、输出低电平状态,以及输出高阻状态

当三态门电路输出为高阻状态时,三态门的输出端相当于开路,对总线上连接的其它器件没有影响

我们可以利用三态门的这个优点对需要通过总线的数据进行分时传送,这样数据的传送就不会出现混乱了

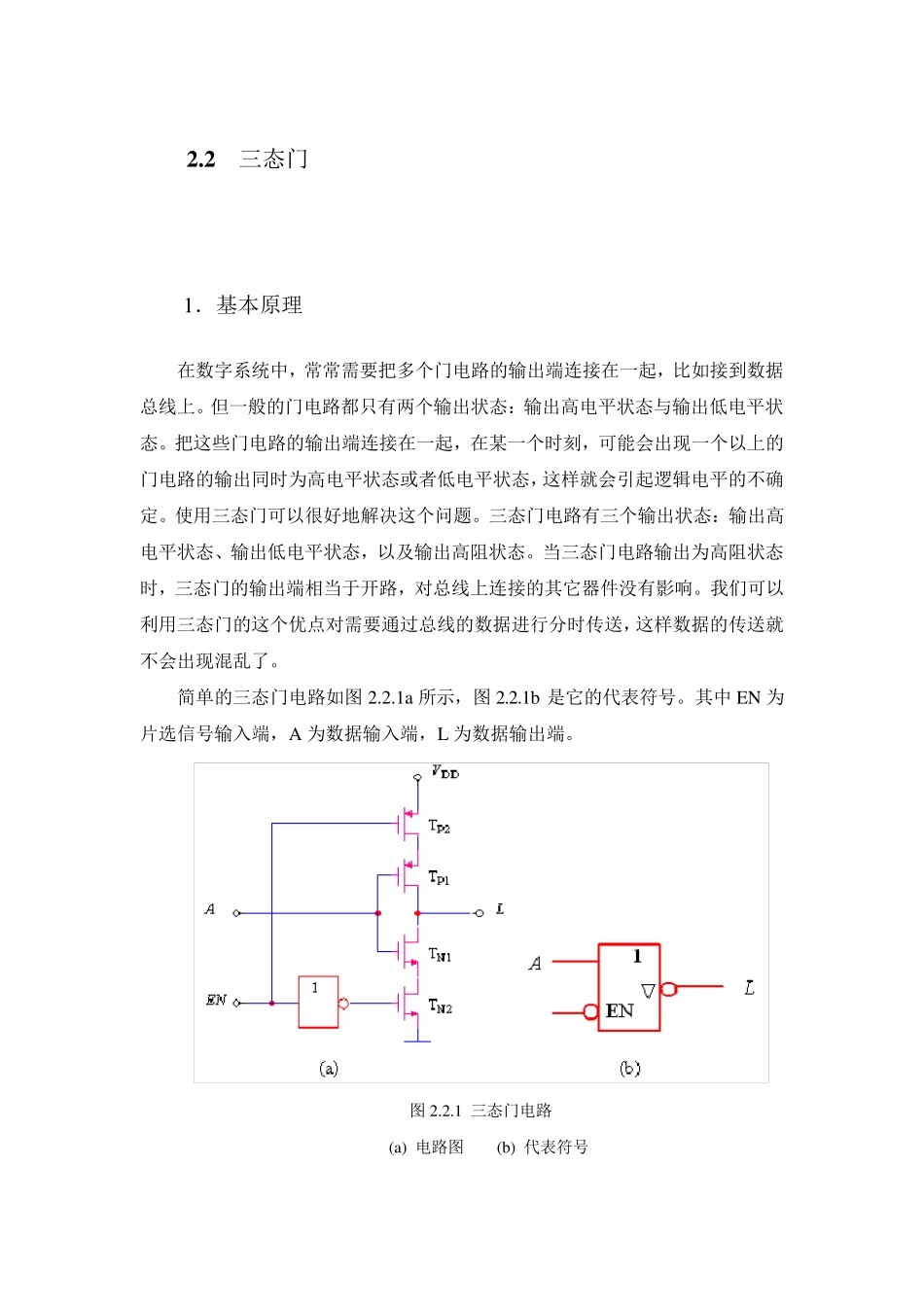

简单的三态门电路如图 2

1a 所示,图 2

1b 是它的代表符号

其中EN 为片选信号输入端,A 为数据输入端,L 为数据输出端

1 三态门电路 (a) 电路图 (b) 代表符号 当EN=0 时,TP2 和TN2 同时导通,为正常的非门,输出L=A ;当EN=1时,TP2 和TN2 同时截止,输出为高阻状态

所以,这是一个低电平有效的三态门

三态门的真值表如表2

由真值表可以得出逻辑表达式:当EN=0时,L=A;当EN=1 时,L=Z

其中Z 表示高阻状态

1 三态门的真值表 EN 数据输入端 输出端L A L 0 1 0 0 1 1 x 高阻 2.实现方案 通过FPGA 来实现三态门的功能有以下几种方式: (1) 用case 语句和if…

else 语句来实现

先判断EN 是否等于1,如果EN等于1,则输出端L=Z;如果不等于1,再判断A 是否等于0,如果等于0,则输出端L=1,如果不等于0,则输出端L=0

(2) 用if…

else 语句来实现

先判断EN 是否等于1,如果EN 等于1,则输出端L=Z;如果不等于1,则