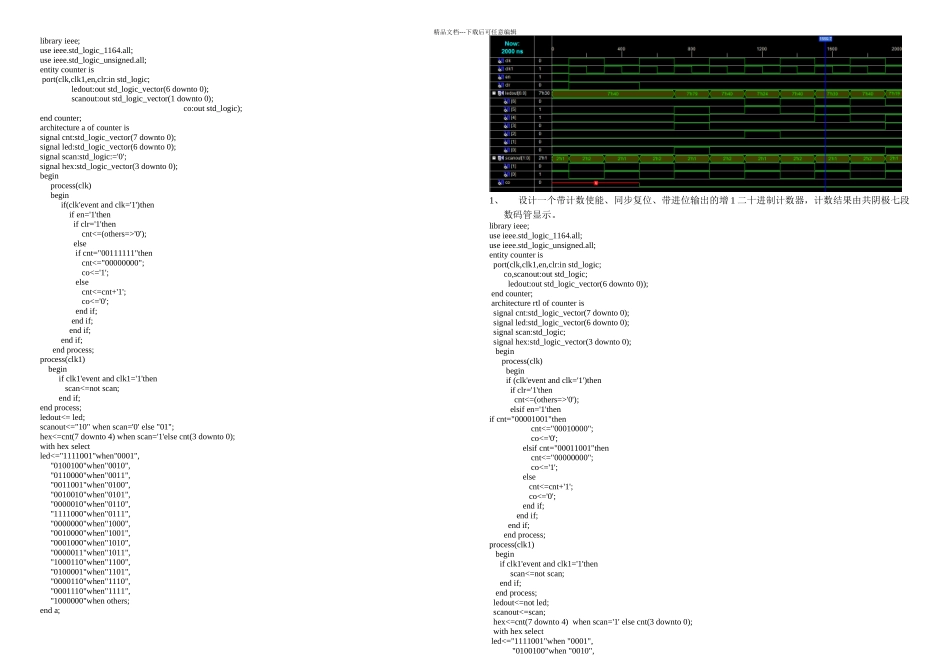

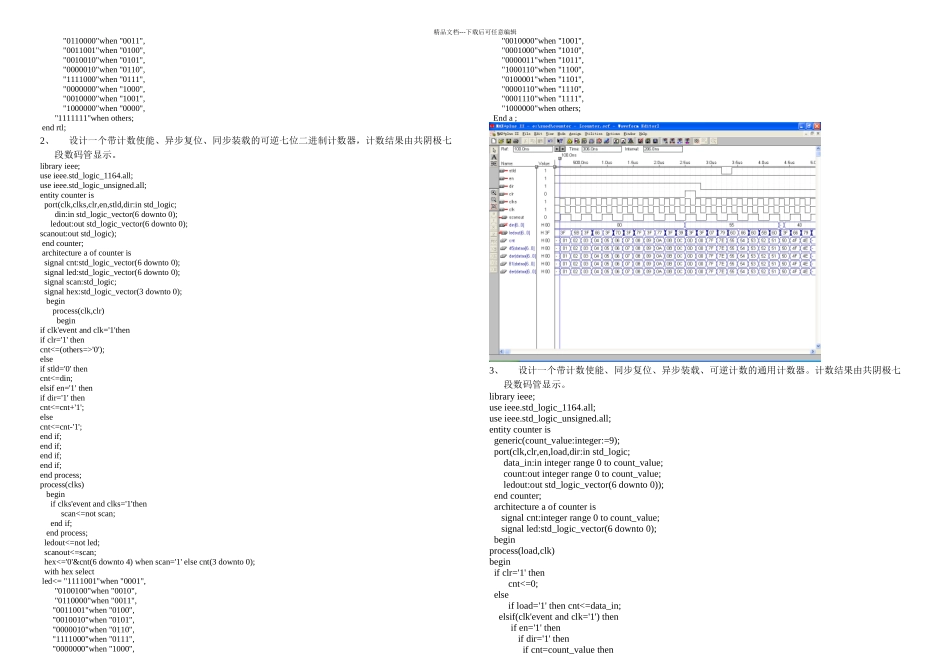

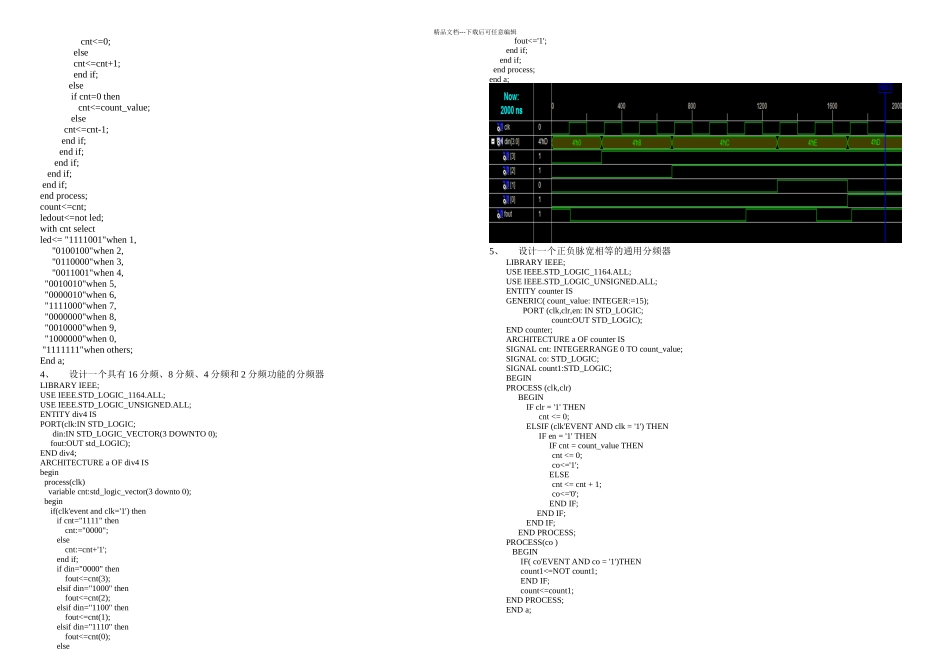

精品文档---下载后可任意编辑library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter is port(clk,clk1,en,clr:in std_logic; ledout:out std_logic_vector(6 downto 0); scanout:out std_logic_vector(1 downto 0);co:out std_logic);end counter;architecture a of counter issignal cnt:std_logic_vector(7 downto 0);signal led:std_logic_vector(6 downto 0);signal scan:std_logic:='0';signal hex:std_logic_vector(3 downto 0);begin process(clk) begin if(clk'event and clk='1')then if en='1'then if clr='1'then cnt<=(others=>'0'); else if cnt="00111111"then cnt<="00000000"; co<='1'; else cnt<=cnt+'1'; co<='0'; end if; end if; end if; end if; end process;process(clk1) begin if clk1'event and clk1='1'then scan<=not scan; end if;end process;ledout<= led;scanout<="10" when scan='0' else "01";hex<=cnt(7 downto 4) when scan='1'else cnt(3 downto 0);with hex selectled<="1111001"when"0001", "0100100"when"0010", "0110000"when"0011", "0011001"when"0100", "0010010"when"0101", "0000010"when"0110", "1111000"when"0111", "0000000"when"1000", "0010000"when"1001", "0001000"when"1010", "0000011"when"1011", "1000110"when"1100", "0100001"when"1101", "0000110"when"1110", "0001110"when"1111", "1000000"when others;end a;1、设计一个带计数使能、同步复位、带进位输出的增 1 二十进制计数器,计数结果由共阴极七段数码管显示。library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter is port(clk,clk1,en,clr:in std_logic; co,scanout:out std_logic; ledout:out std_logic_vector(6 downto 0)); end counter; architecture rtl of counter is signal cnt:std_logic_vector(7 downto 0); signal led:std_logic_vector(6 downto 0); signal scan:std_logic; signal hex:std_logic_vector(3 downto 0); begin process(clk) begin if (clk'event and clk='1')then if clr='1'then cnt<=(others=>'0'); elsif en='1'thenif cnt="00001001"then cnt<="0001000...