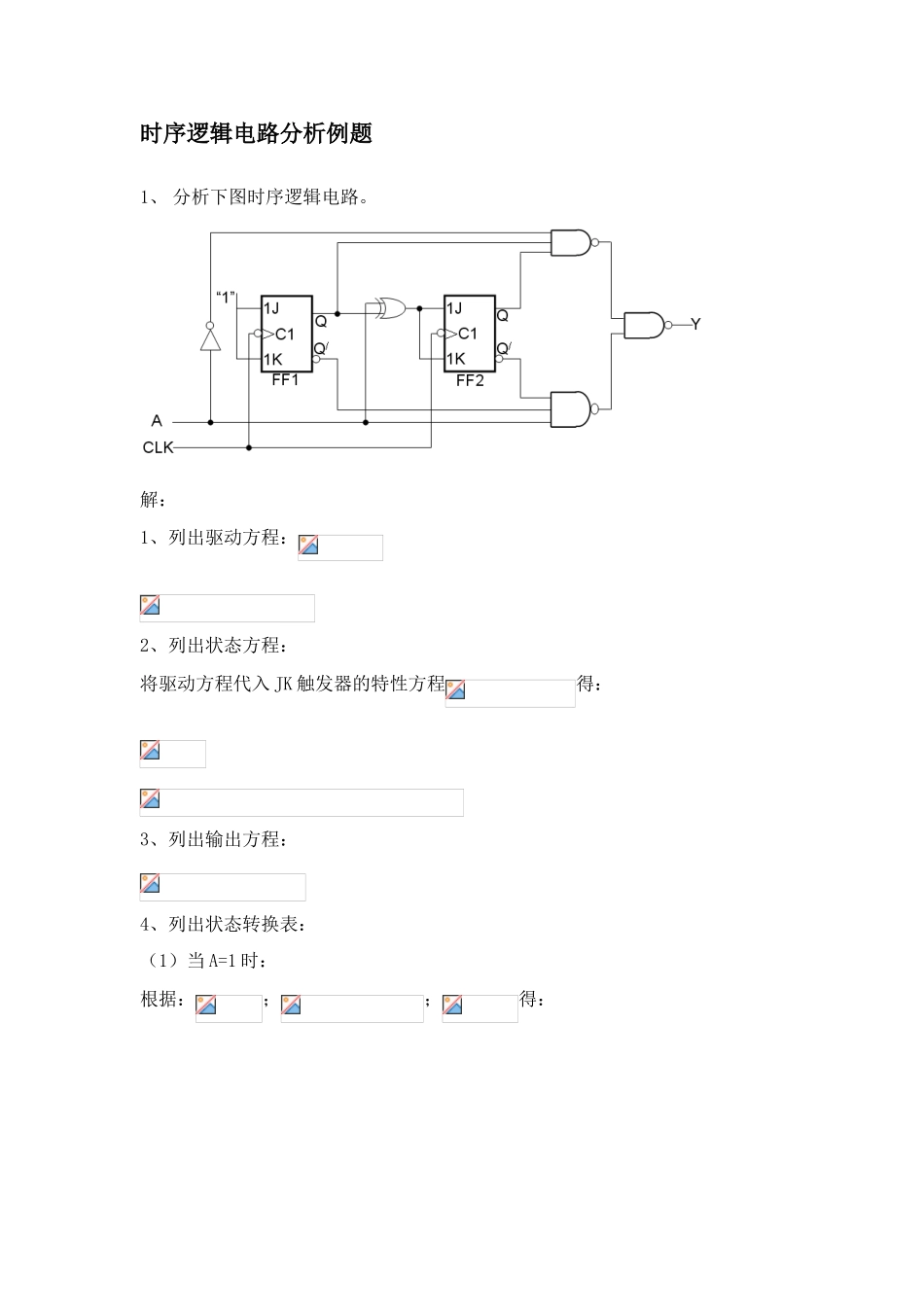

时序逻辑电路分析例题1、 分析下图时序逻辑电路

解:1、列出驱动方程:2、列出状态方程:将驱动方程代入 JK 触发器的特性方程得:3、列出输出方程:4、列出状态转换表:(1)当 A=1 时:根据:;;得:(2)当 A=0 时:根据:;;得:5、画状态转换图:6、说明电路实现的逻辑功能:此电路是一个可逆 4 进制(二位二进制)计数器,CLK 是计数脉冲输入端,A 是加减控制端,Y 是进位和借位输出端

当控制输入端 A 为低电平 0 时,对输入的脉冲进行加法计数,计满 4 个脉冲,Y 输出端输出一个高电平进位信号

当控制输入端 A 为高电平 1 时,对输入的脉冲进行减法计数,计满 4 个脉冲,Y 输出端输出一个高电平借位信号

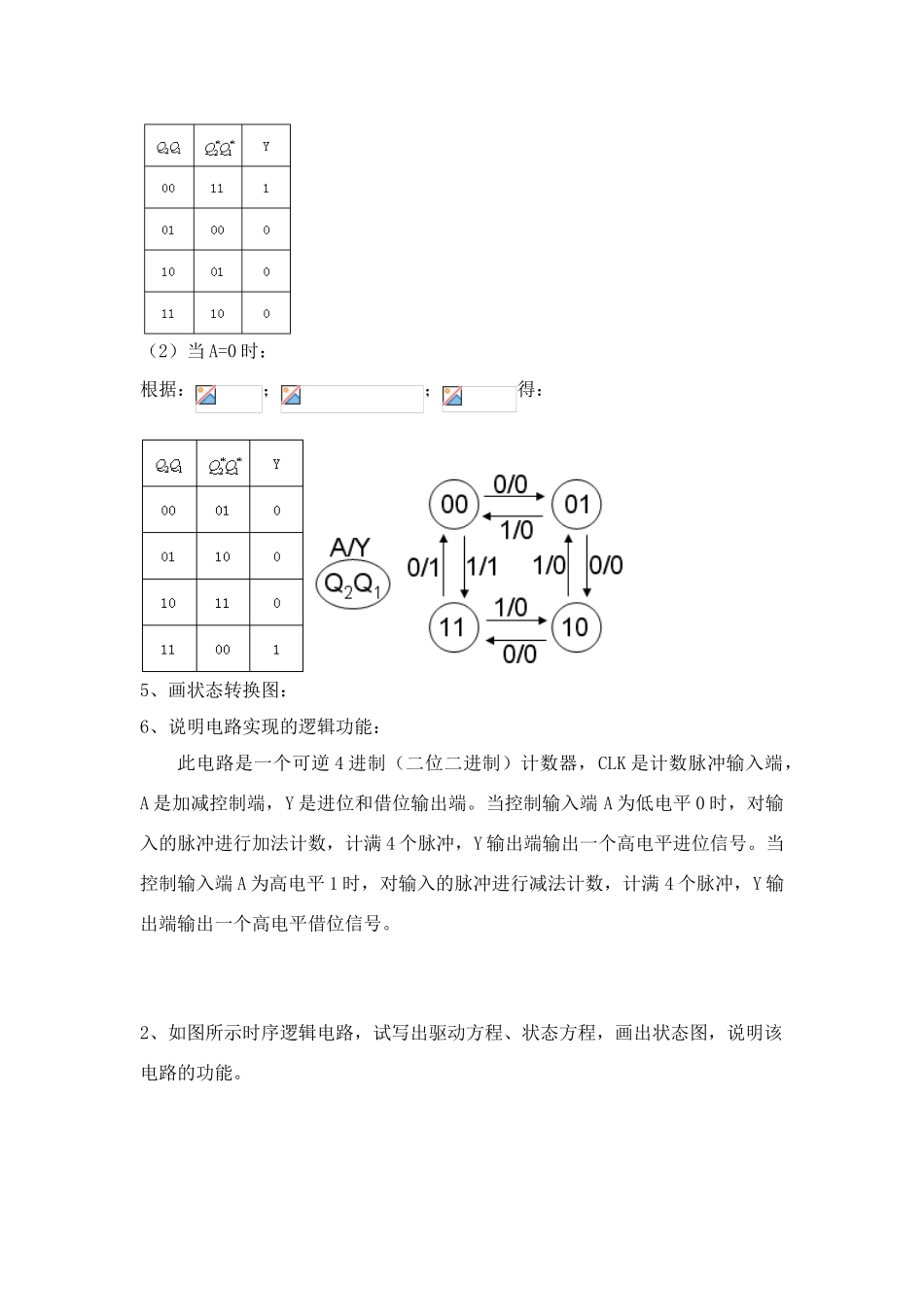

2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能

解:驱动方程 状态方程输出方程 1、状态转换表,如表所示

状态转换图,略

2、这是一个 3 进制加减计数器,当 X=0 时为加计数器,计满后通过 Z向高位进位;X=1 时为减计数器,计满后通过 Z 向高位借位;能自启动

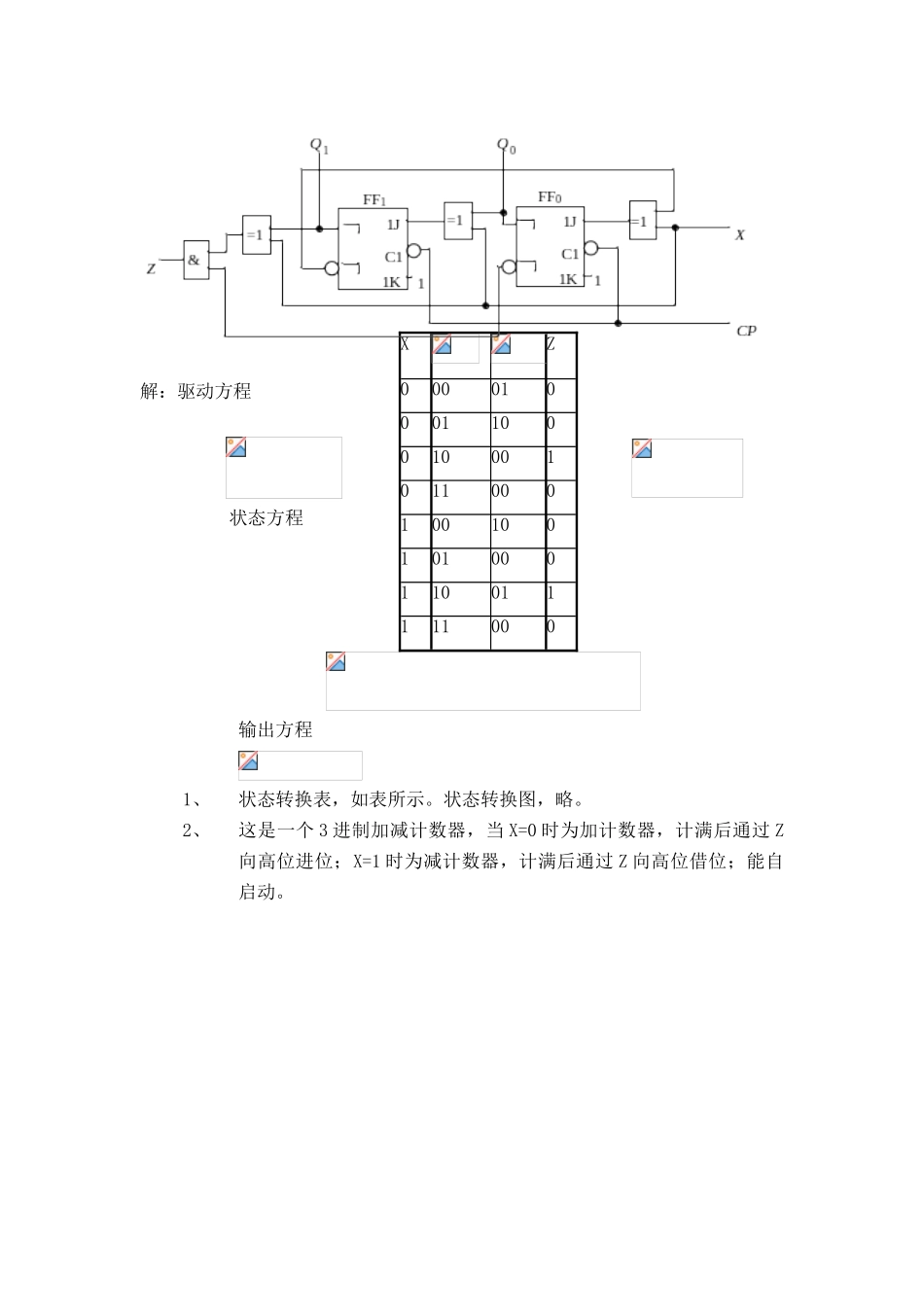

XZ000010001100010001011000100100101000110011111000例 3、分析下图所示的计数器电路(设初始状态是 0),要求(1) 画出状态转换图

(2) 画出时序图

(3) 说明是多少进制计数器

答:(1)(2)时序图4、分析下图所示时序逻辑电路,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路实现的的逻辑功能

A 为输入变量

〉1J1KC1QFF0〉1J1KC1QFF11CPQ0Q1CPQ0Q1解:(1)列写方程驱动方程:触发器的驱动方程为: (2)列写方程驱动方程:触发器的特性方程为:将驱动方程代入特性方程可得状态方程为:(3)列写输出方程: (4)列出状态转换表:当 A=1 时:根据:;;得:当