CIC 插值滤波器设计指导2007 年 11 月 12 日杜伟韬0

1 版修订记录:设计目标设计一个 16 倍的插值的 CIC 滤波器 IP,名称为 CIC16I

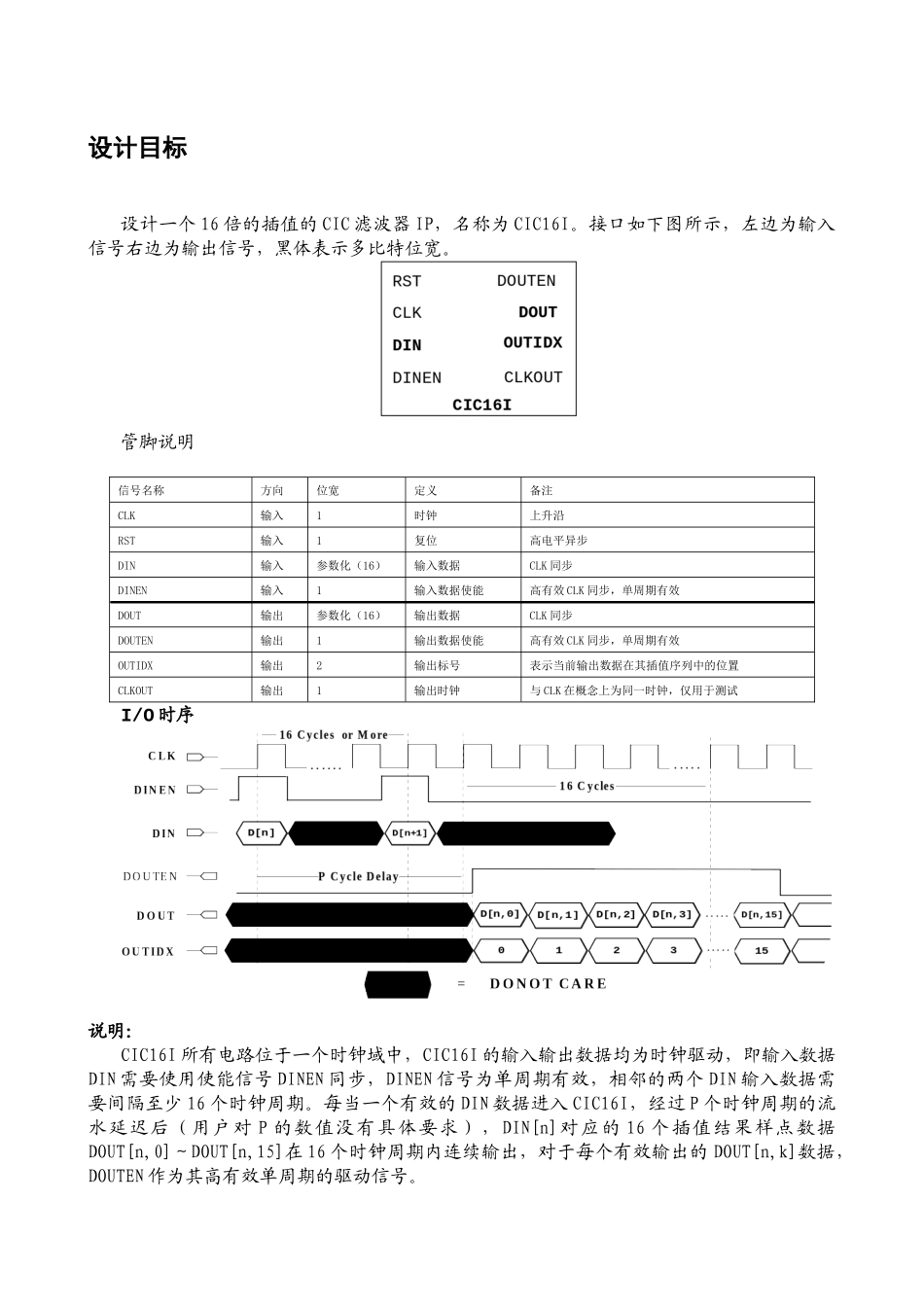

接口如下图所示,左边为输入信号右边为输出信号,黑体表示多比特位宽

管脚说明信号名称方向位宽定义备注CLK输入1时钟上升沿RST输入1复位高电平异步DIN输入参数化(16)输入数据CLK 同步DINEN输入1输入数据使能高有效 CLK 同步,单周期有效DOUT输出参数化(16)输出数据CLK 同步DOUTEN输出1输出数据使能高有效 CLK 同步,单周期有效OUTIDX输出2输出标号表示当前输出数据在其插值序列中的位置CLKOUT输出1输出时钟与 CLK 在概念上为同一时钟,仅用于测试I/O 时序说明:CIC16I 所有电路位于一个时钟域中,CIC16I 的输入输出数据均为时钟驱动,即输入数据DIN 需要使用使能信号 DINEN 同步,DINEN 信号为单周期有效,相邻的两个 DIN 输入数据需要间隔至少 16 个时钟周期

每当一个有效的 DIN 数据进入 CIC16I,经过 P 个时钟周期的流水延迟后(用户对 P 的数值没有具体要求),DIN[n]对应的 16 个插值结果样点数据DOUT[n,0]~DOUT[n,15]在 16 个时钟周期内连续输出,对于每个有效输出的 DOUT[n,k]数据,DOUTEN 作为其高有效单周期的驱动信号

CIC16I 的输入、输出数据均为 16 比特有符号数,内部节点数据宽度不限,但是要求尽量达到较高的计算精度

设计成果设计过程完成后,应当还有以下设计资料

参考文献 需求分析和理论算法推导报告 定点算法讨论及仿真结果报告 电路结构设计报告 用户手册与测试报告 定点仿真代码 Testbenc 代码 RTL 代码设计阶段规划整个设计流程分为资料阅读阶段,需求分析和理论