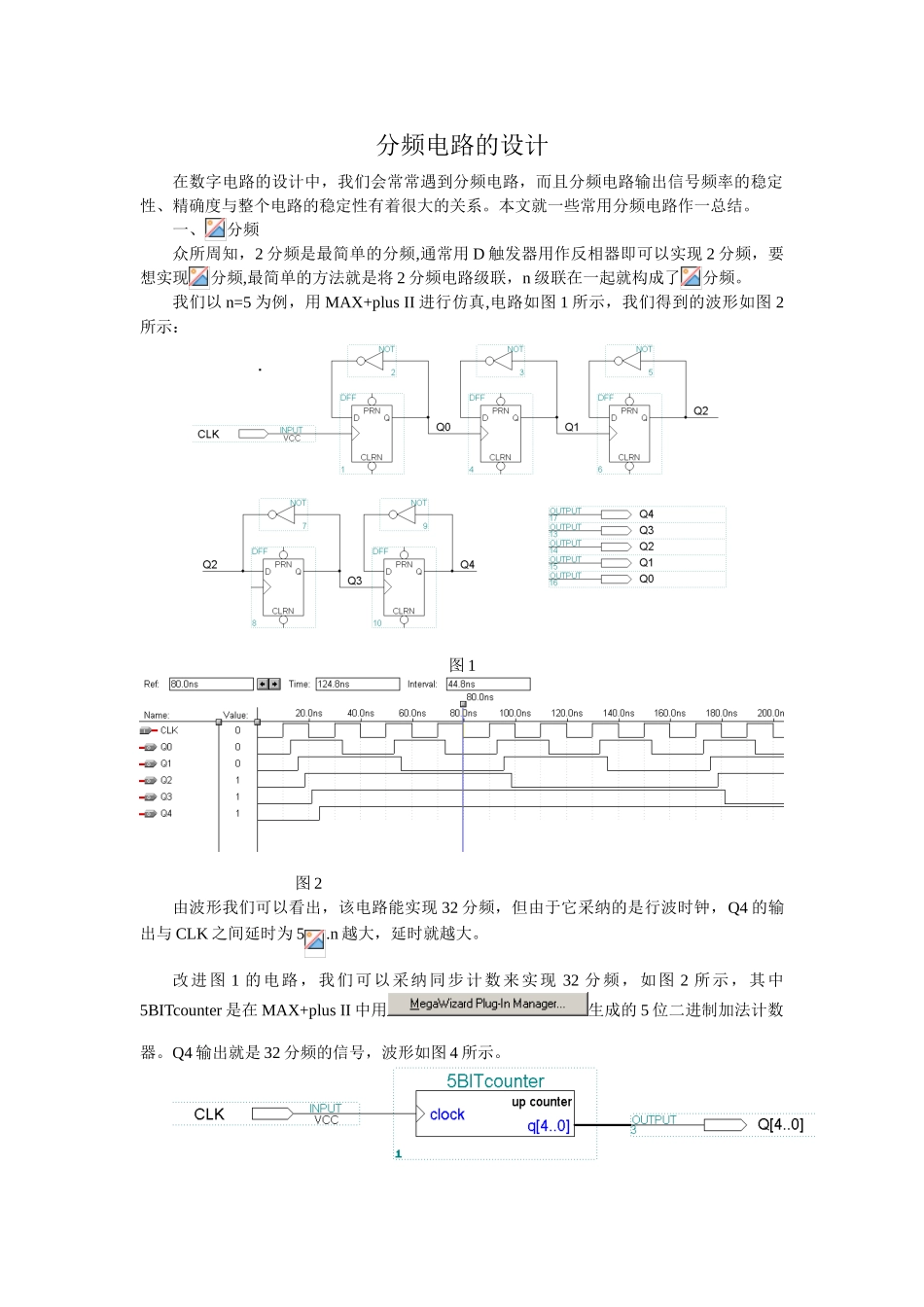

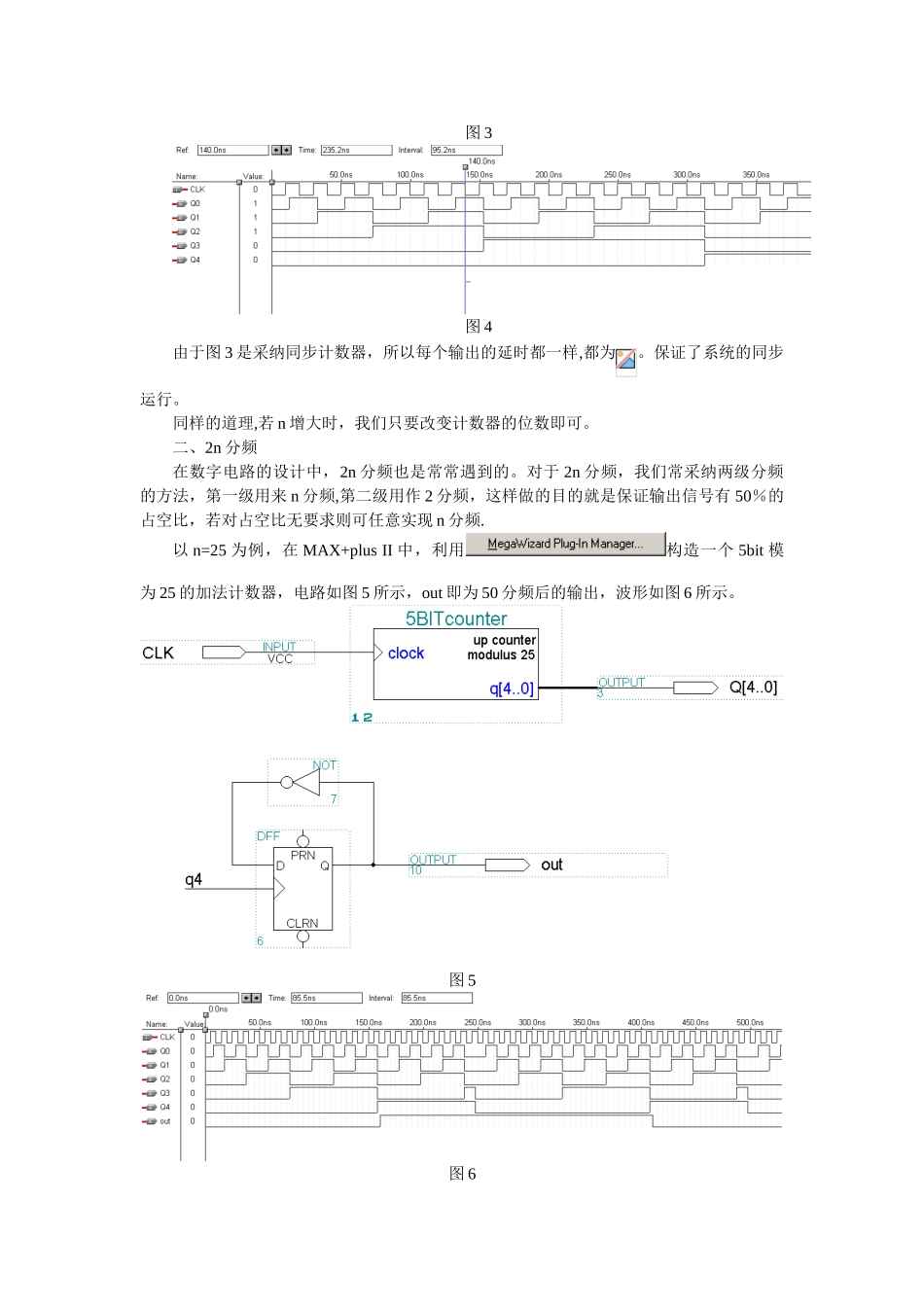

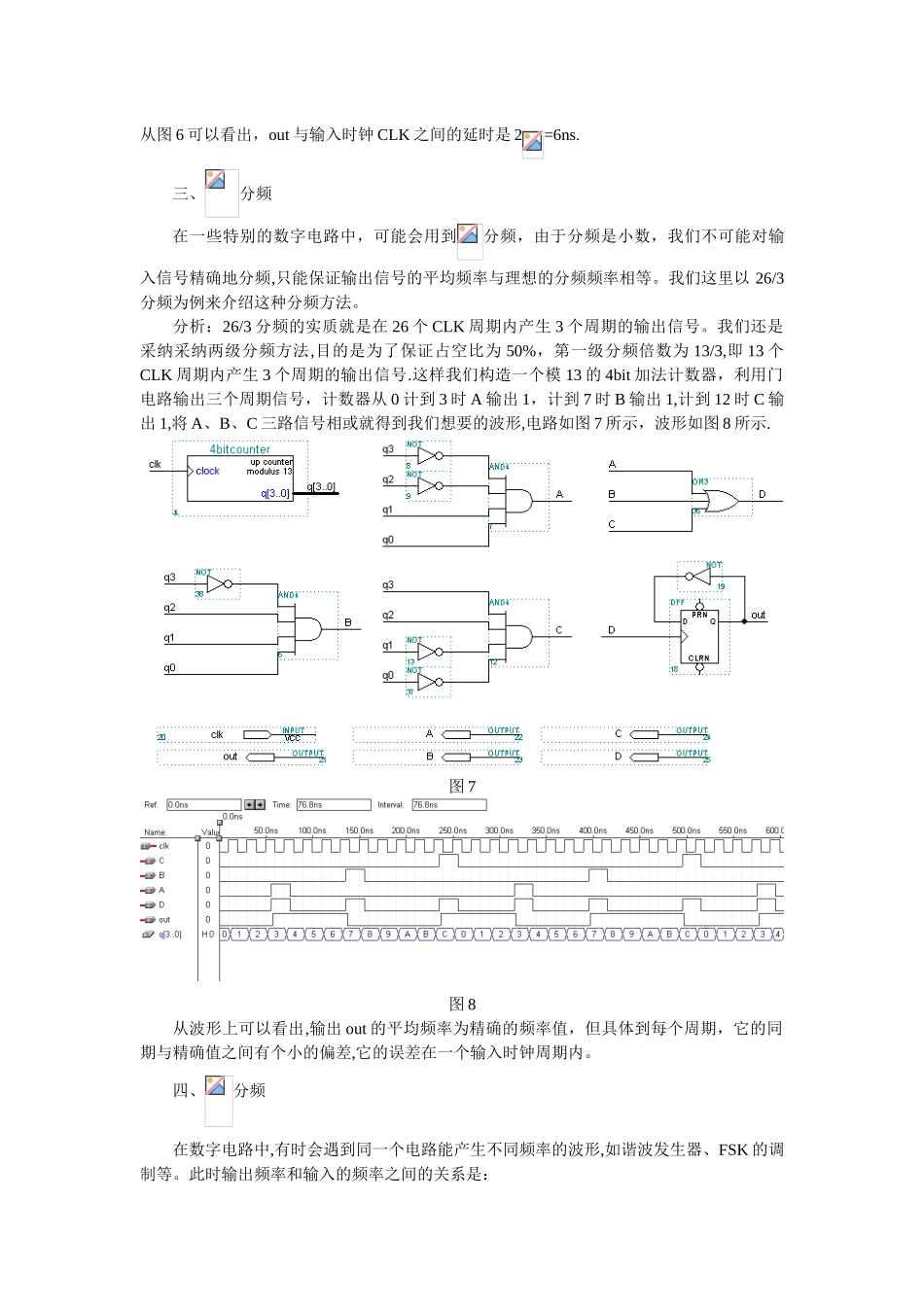

分频电路的设计在数字电路的设计中,我们会常常遇到分频电路,而且分频电路输出信号频率的稳定性、精确度与整个电路的稳定性有着很大的关系。本文就一些常用分频电路作一总结。一、分频众所周知,2 分频是最简单的分频,通常用 D 触发器用作反相器即可以实现 2 分频,要想实现分频,最简单的方法就是将 2 分频电路级联,n 级联在一起就构成了分频。我们以 n=5 为例,用 MAX+plus II 进行仿真,电路如图 1 所示,我们得到的波形如图 2所示:图 1 图 2由波形我们可以看出,该电路能实现 32 分频,但由于它采纳的是行波时钟,Q4 的输出与 CLK 之间延时为 5.n 越大,延时就越大。改进图 1 的电路,我们可以采纳同步计数来实现 32 分频,如图 2 所示,其中5BITcounter 是在 MAX+plus II 中用生成的 5 位二进制加法计数器。Q4 输出就是 32 分频的信号,波形如图 4 所示。图 3图 4由于图 3 是采纳同步计数器,所以每个输出的延时都一样,都为。保证了系统的同步运行。同样的道理,若 n 增大时,我们只要改变计数器的位数即可。二、2n 分频在数字电路的设计中,2n 分频也是常常遇到的。对于 2n 分频,我们常采纳两级分频的方法,第一级用来 n 分频,第二级用作 2 分频,这样做的目的就是保证输出信号有 50%的占空比,若对占空比无要求则可任意实现 n 分频.以 n=25 为例,在 MAX+plus II 中,利用构造一个 5bit 模为 25 的加法计数器,电路如图 5 所示,out 即为 50 分频后的输出,波形如图 6 所示。图 5图 6从图 6 可以看出,out 与输入时钟 CLK 之间的延时是 2=6ns.三、分频在一些特别的数字电路中,可能会用到分频,由于分频是小数,我们不可能对输入信号精确地分频,只能保证输出信号的平均频率与理想的分频频率相等。我们这里以 26/3分频为例来介绍这种分频方法。分析:26/3 分频的实质就是在 26 个 CLK 周期内产生 3 个周期的输出信号。我们还是采纳采纳两级分频方法,目的是为了保证占空比为 50%,第一级分频倍数为 13/3,即 13 个CLK 周期内产生 3 个周期的输出信号.这样我们构造一个模 13 的 4bit 加法计数器,利用门电路输出三个周期信号,计数器从 0 计到 3 时 A 输出 1,计到 7 时 B 输出 1,计到 12 时 C 输出 1,将 A、B、C 三路信号相或就得到我们想要的波形,电路如图 7 所示,波形如图 8 所示.图 7图 8从波形上可...