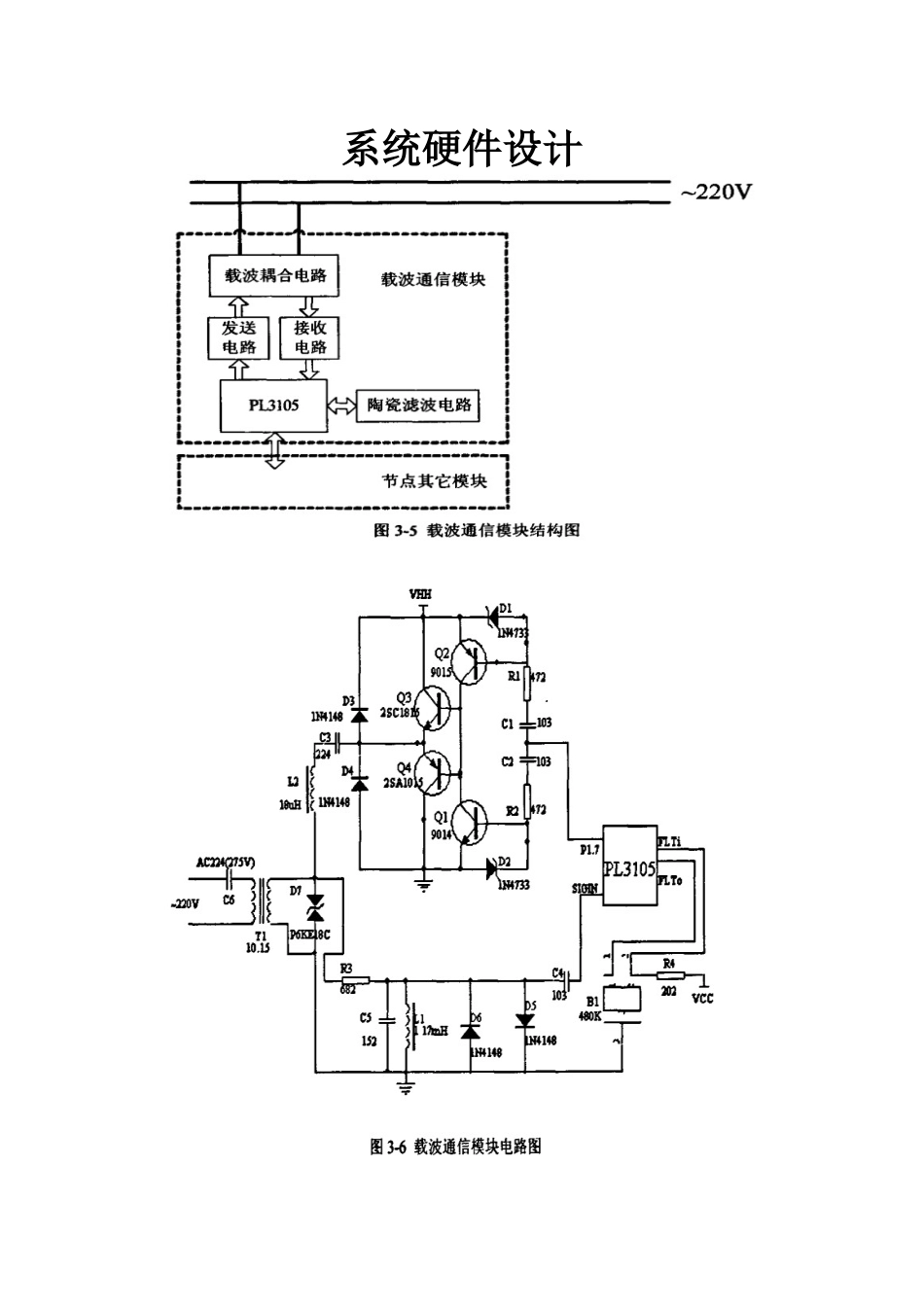

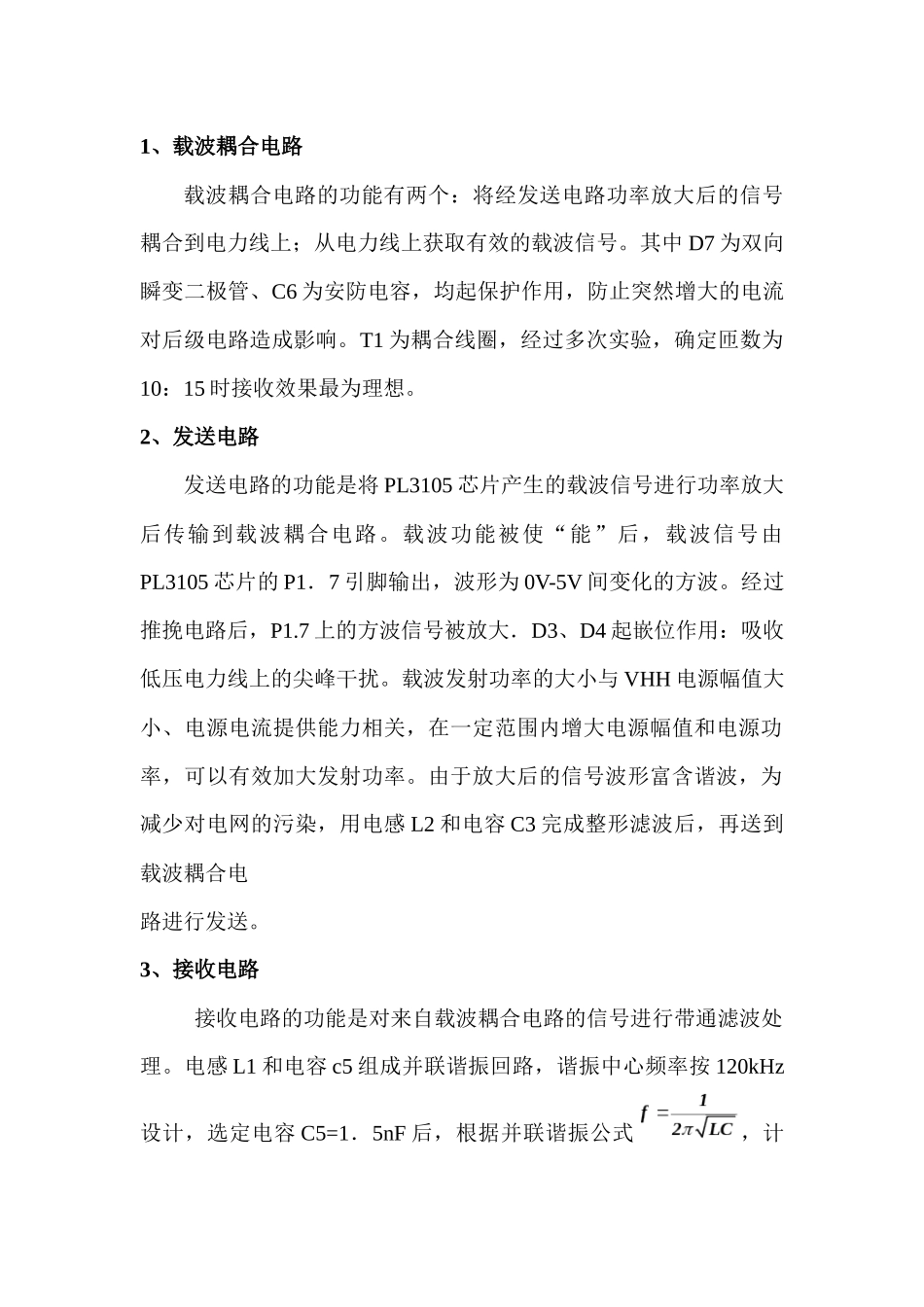

系统硬件设计1、载波耦合电路载波耦合电路的功能有两个:将经发送电路功率放大后的信号耦合到电力线上;从电力线上获取有效的载波信号

其中D7为双向瞬变二极管、C6为安防电容,均起保护作用,防止突然增大的电流对后级电路造成影响

T1为耦合线圈,经过多次实验,确定匝数为10:15时接收效果最为理想

2、发送电路发送电路的功能是将PL3105芯片产生的载波信号进行功率放大后传输到载波耦合电路

载波功能被使“能”后,载波信号由PL3105芯片的P1.7引脚输出,波形为0V-5V间变化的方波

经过推挽电路后,P1

7上的方波信号被放大.D3、D4起嵌位作用:吸收低压电力线上的尖峰干扰

载波发射功率的大小与VHH电源幅值大小、电源电流提供能力相关,在一定范围内增大电源幅值和电源功率,可以有效加大发射功率

由于放大后的信号波形富含谐波,为减少对电网的污染,用电感L2和电容C3完成整形滤波后,再送到载波耦合电路进行发送

3、接收电路接收电路的功能是对来自载波耦合电路的信号进行带通滤波处理

电感L1和电容c5组成并联谐振回路,谐振中心频率按120kHz设计,选定电容C5=1.5nF后,根据并联谐振公式,计算得到L1=1

二极管D5、D6将接收到的信号嵌位在±0.7V

接收信号经过电容C4后引入PL3105芯片内部进行混频处理SIGIN处的信号将被上拉后平移到2

7V,以便于后续处理

4PL3105载波通信的扩频解扩工作完全由PL3105内部的硬件电路来实现

发送时,PL3105用伪随机码序列将信号扩展到较宽的频带上进行发送;接收时,PL3105在捕获载波信号后用同步的伪随机码序列对信息进行恢复

其中,关键过程是载波信号的捕获和同步,其余步骤均按前文所述的标准过程进行

捕获是接收端在精确同步前搜索接收信号,使要被接收的信号的伪随机码序列与本地的伪随机码序列的相位保持在一个扩