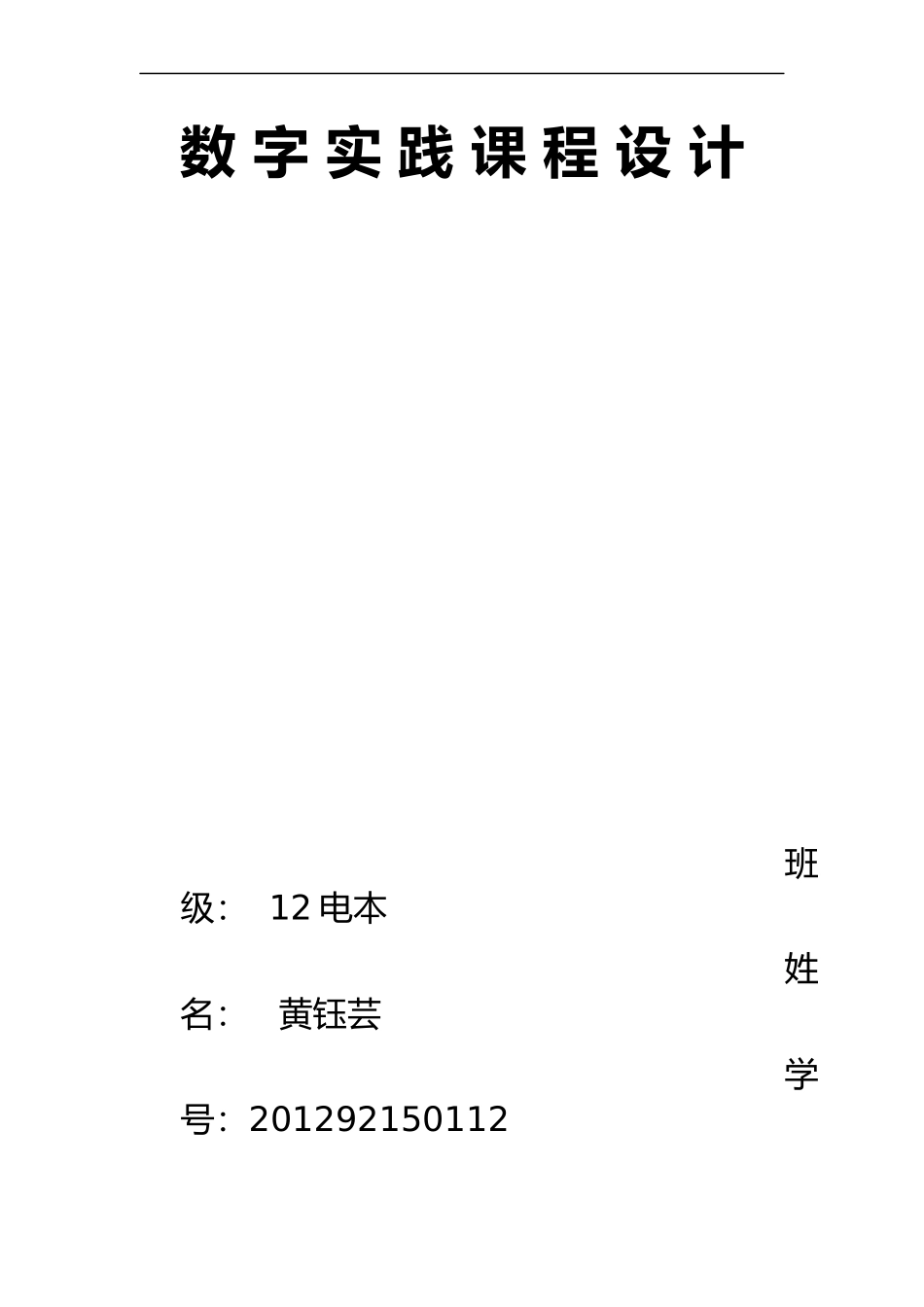

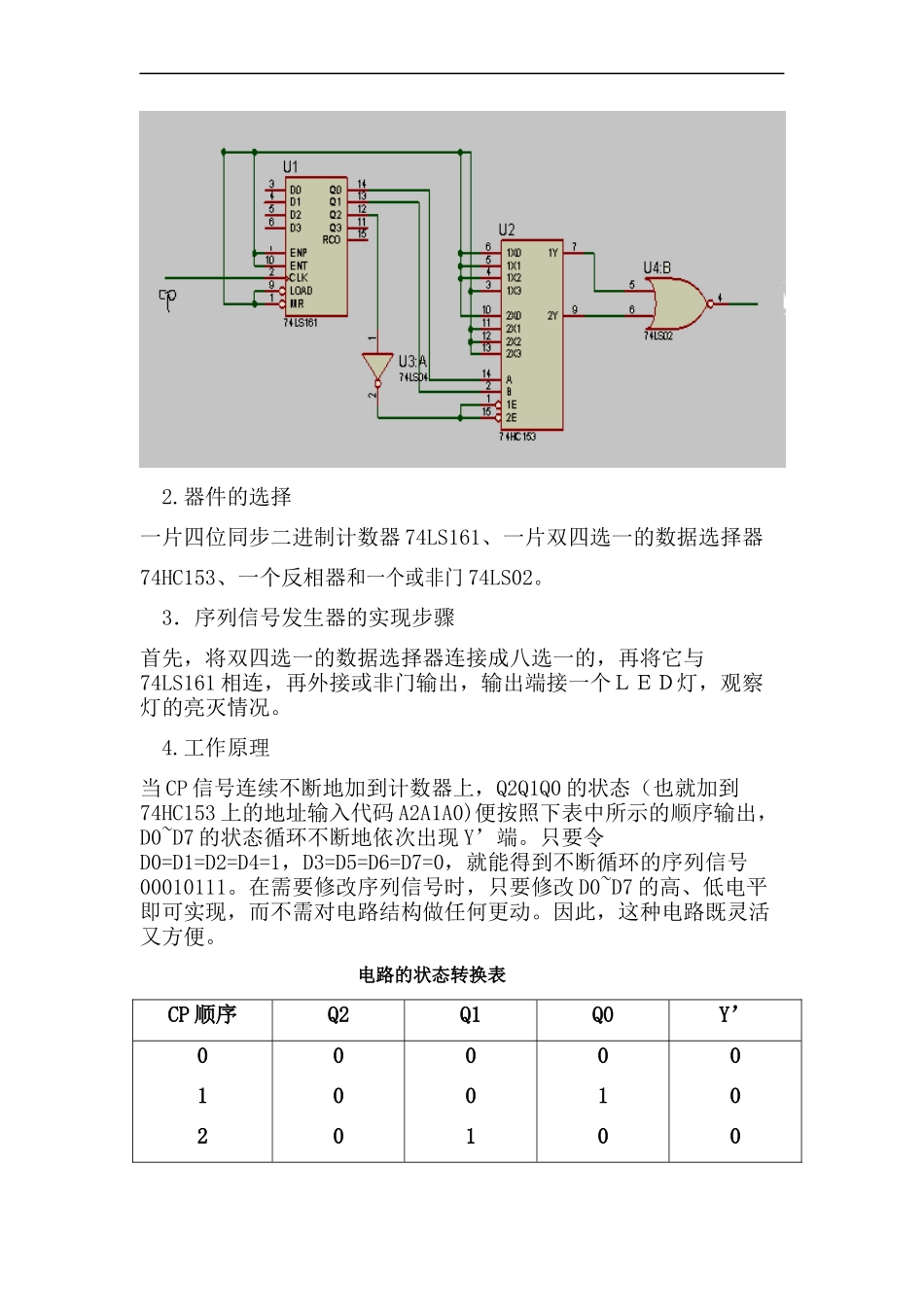

数字实践课程设计班级:12电本姓名:黄钰芸学号:201292150112指导教师:崔用明用74LS161和四选一数据选择器设计一个输出序列为00011101的序列信号发生器一.摘要序列信号发生器的构成方法有很多种,一般是用组合逻辑电路和时序逻辑电路的方法设计,电路的设计相对来讲是比较简单,直观。英文摘要(Translation):Sequenceusingatriggersignalgeneratorplusgeneralcombinationallogiccircuitsandsequentiallogiccircuitsdesigned,circuitdesignandimplementationmorecomplex.键词:序列信号发生器、双二、设计要求:1.学会构建序列信号发生器的基本方法。2.掌握对序列信号发生器序列信号的测试分析方法。3.用74LS161和四选一数据选择器设计一个输出序列为00011101的序列信号发生器。三、设计步骤:1.电路原理图:2.器件的选择一片四位同步二进制计数器74LS161、一片双四选一的数据选择器74HC153、一个反相器和一个或非门74LS02。3.序列信号发生器的实现步骤首先,将双四选一的数据选择器连接成八选一的,再将它与74LS161相连,再外接或非门输出,输出端接一个LED灯,观察灯的亮灭情况。4.工作原理当CP信号连续不断地加到计数器上,Q2Q1Q0的状态(也就加到74HC153上的地址输入代码A2A1A0)便按照下表中所示的顺序输出,D0~D7的状态循环不断地依次出现Y’端。只要令D0=D1=D2=D4=1,D3=D5=D6=D7=0,就能得到不断循环的序列信号00010111。在需要修改序列信号时,只要修改D0~D7的高、低电平即可实现,而不需对电路结构做任何更动。因此,这种电路既灵活又方便。电路的状态转换表CP顺序Q2Q1Q0Y’012000001010000345678011110100110101010101110四位同步二进制计数器74LS161的功能表CPRD’LD’EPET工作状态XXX01111X0111XX0X1XX101置零预置数保持保持(C=0)计数四位同步二进制计数器74LS161的时序图四位同步二进制计数器74LS161的引脚图四.仿真经过仿真,由LED的亮灭情况发现实现了用74LS161和四选一数据选择器设计一个输出序列为00011101的序列信号发生器。五.心得体会通过本次实践,我更深刻的理解了用74LS161和四选一数据选择器设计一个输出序列为00011101的序列信号发生器。掌握了数字电路设计的基本方法,设计步骤和综合能力。这次实践让我知道“学无止境”。D03Q014D14Q113D25Q212D36Q311RCO15ENP7ENT10CLK2LOAD9MR1U174LS1611X061Y71X151X241X332X0102Y92X1112X2122X313A14B21E12E15U274HC153564U4:B74LS0212U3:A74LS04U1(CLK)D3LED-RED